Analoge basisprincipes - Deel 5: Aanpak van moeilijke invoerproblemen voor de SAR ADC

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2020-10-28

Opmerking van de editor: Analoge naar digitale convertors (ADC's) verbinden de analoge met de digitale wereld, en zijn dus een fundamenteel onderdeel van elk elektronisch systeem dat verbinding maakt met de echte wereld. Ze zijn ook een belangrijke bepalende factor voor de prestaties van een systeem. Deze serie verkent de fundamenten van ADC's, hun verschillende types en hun toepassing. In deel 1 van deze serie over de analoge basisprincipes worden SAR ADC's besproken. Deel 2 bespreekt delta-sigma-omvormers. In deel 3 kijkt naar pijplijn-ADC's. Deel 4 laat zien hoe delta-sigma ADC's ultralage-ruisresultaten kunnen genereren. Deel 5 gaat hier in op de moeilijke problemen met de invoer voor SAR ADC's.

Veel data-acquisitie-, industriële besturings- en instrumentatietoepassingen vereisen een ultrasnelle analoog-digitaal-convertor (ADC) wanneer een SAR-convertor (successive-approximation register) perfect geschikt is. Het is echter essentieel om ervoor te zorgen dat de externe circuits rond de SAR-convertor ook geschikt zijn voor een succesvolle conversie. De cruciale terminals die speciale zorg nodig hebben voor de SAR-convertor zijn de analoge signaalinputs - als ze onbeheerd worden gelaten, kunnen deze ingangspennen stabiliteitsproblemen en capacitieve lading "kickbacks" veroorzaken die kunnen leiden tot onnauwkeurige conversies en een lange signaalacquisitietijd.

De oplossing voor een nauwkeurige regeling van het ingangssignaal voor SAR-convertortoepassingen ligt in het aansturen van operationele versterkers (op-ampers). Deze apparaten, ondersteund door de juiste uitgangsweerstands- en condensatorwaarden, vormen de basis van een uiterst nauwkeurige, robuuste oplossing voor 16-bits en 20-bits SAR-convertorsystemen met hoge resolutie.

In dit artikel wordt kort ingegaan op de kwesties die samenhangen met het bereiken van stabiele en nauwkeurige SAR ADC-conversies. Het introduceert vervolgens een geschikte versterker voor het besturen van een SAR ADC en laat zien hoe de noodzakelijke input driver circuits te implementeren. Oplossingen van Analog Devices zullen als voorbeeld worden gebruikt.

SAR ADC-ingangscircuit

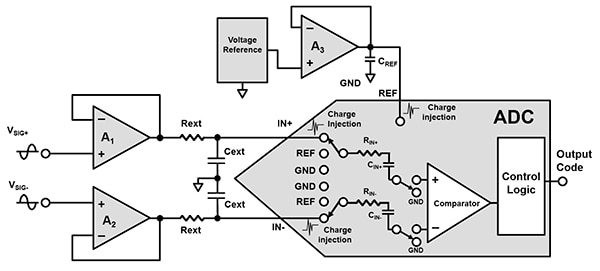

De SAR ADC driver circuits hebben op-amps (A1 enA2) die de ADC scheiden van hun signaalbronnen (Afbeelding 1). In deze schakeling houdt Rext de versterker stabiel door de eindtrap van de versterker te "isoleren" van de ADC capacitieve belasting (CIN+ en CIN-) en Cext. Cext en CREF bieden een bijna perfecte ingangsbron voor de ADC die de schakelende ladingsinjectie van de IN+, IN- en REF ingangsklemmen absorbeert. De ingangsklemmen (IN+, IN-) volgen de spanning van het ingangssignaal (VSIG+, VSIG-) gedurende de acquisitietijd van de convertor en zorgen voor de lading van de ADC's ingangsbemonsteringscondensators, CIN+ en CIN-.

Afbeelding 1: In deze schakeling "isoleert" Rext Cext van de versterkereindtrap. Cext en CREF voorzien in laadreservoirs voor de differentiële SAR ADC tijdens de bemonsteringsperiode. (Bron afbeelding: DigiKey)

Afbeelding 1: In deze schakeling "isoleert" Rext Cext van de versterkereindtrap. Cext en CREF voorzien in laadreservoirs voor de differentiële SAR ADC tijdens de bemonsteringsperiode. (Bron afbeelding: DigiKey)

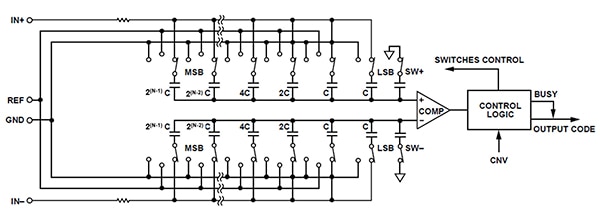

Kijkend naar het interieur van de ADC met behulp van Analog Device's AD7915 (16-bit) en AD4021 (20-bit) SAR ADC's als voorbeelden, kan men zien dat het gebruik van een lading herverdeling digitaal-naar-analoog converter (DAC). De capacitieve DAC heeft twee identieke arrays van binairgewogen condensators. Deze arrays worden aangesloten op de niet-inverterende en inverterende vergelijkingsingangen (Afbeelding 2).

Afbeelding 2: Een vereenvoudigd AD7915 en AD4021 gebaseerd schema van een SAR ADC, waarbij N gelijk is aan het aantal bits van de convertor. (Bron afbeelding: Gewijzigd door DigiKey uit origineel materiaal van Analog Devices)

Afbeelding 2: Een vereenvoudigd AD7915 en AD4021 gebaseerd schema van een SAR ADC, waarbij N gelijk is aan het aantal bits van de convertor. (Bron afbeelding: Gewijzigd door DigiKey uit origineel materiaal van Analog Devices)

Tijdens de acquisitiefase schakelen de ingangen (IN+ en IN-) over op de capacitieve array. Bovendien sluiten SW+ en SW- de minst significante bit (LSB) condensators aan de massa (GND). In deze toestand worden de condensatorarrays de bemonsteringscondensators, die de IN+ en IN-analoge signalen krijgen. Na afronding van de acquisitiefase gaat de CNV-input in de besturingslogica (rechterzijde) hoog om de conversiefase te starten.

De conversiefase begint met het openen van SW+ en SW- en het omschakelen van de twee condensator-arrays naar GND. In deze configuratie zorgt de opgevangen IN+ en IN- differentieelspanning ervoor dat de comparator uit balans raakt. De ladingsherverdeling DAC schakelt elk element van de condensatorarray methodisch van het meest significante bit (MSB) naar LSB, tussen GND en REF. De vergelijkingsingang varieert met binairgewogen spanningsstappen (VREF/2N-1, VREF/2N-2 VREF/4, VREF/2). De besturingslogica schakelt de schakelaars van de MSB naar de LSB, waardoor de vergelijker weer in een gebalanceerde toestand komt. Na afloop van dit proces keert de ADC terug naar de acquisitiefase en de controlelogica genereert de ADC-uitvoercode.

Injectie van de ingangslading, stabiliteit van het circuit en het aandrijven van de AD7915 ADC

Een cruciaal onderdeel van het conversieproces is het verkrijgen van een nauwkeurige ingangsspanning. Het ADC-dataconversieproces verloopt soepel wanneer de aandrijfversterker de ingangscondensatoren, CIN+ en CIN- nauwkeurig oplaadt, met behoud van de stabiliteit tot het einde van de ADC-acquisitietijd. Het probleem voor ontwerpers is dat de ADC's ingangsklem een capaciteit (CIN+, CIN-) introduceert, evenals schakelruis of "kickback" laadinjectie voor de aandrijvende versterker om te beheren.

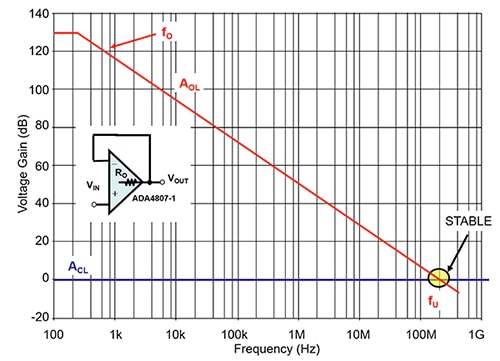

Een versterkercircuit Bode plot schat snel de stabiliteit van het circuit in. De Bode-plottool benadert de omvang van de open-loop en de closed-loop versterkingsfuncties van een versterker (Afbeelding 3).

Afbeelding 3: De open en gesloten-lus overdrachtsfunctie van de versterker in Afbeelding 1, zonder Rext en Cext als versterkerbelasting en de volgende SAR ADC. (Bron afbeelding: DigiKey)

Afbeelding 3: De open en gesloten-lus overdrachtsfunctie van de versterker in Afbeelding 1, zonder Rext en Cext als versterkerbelasting en de volgende SAR ADC. (Bron afbeelding: DigiKey)

De y-as kwantificeert de open-loop versterkingsfactor (AOL) van de versterker en de closed-loop versterkingsfactor (ACL) van de versterkerkring, waarbij de AOL-curve van de versterker begint bij 130 decibel (dB) en de closed-loop versterkingsfactor,ACL, gelijk is aan 0 dB. De eenheden langs de x-as kwantificeren logaritmisch de open en gesloten-lus versterkingsfrequentie van 100 Hertz (Hz) tot 1 gigahertz (GHz).

In Afbeelding 3 gaat de DC open-loop gain van de versterker bij ongeveer 220 Hz (fO) omlaag van 130 dB met een snelheid van -20 dB/decadium. Naarmate de frequentie toeneemt, gaat deze dempingssnelheid verder dan 0 dB bij ongeveer 180 megahertz (MHz). Aangezien deze curve een enkelpolig systeem vertegenwoordigt, is de crossover-frequentie, fU, is gelijk aan het versterkingsbandbreedteproduct van de eenheidsversterker-stabiele versterker(GBWP). Dit perceel vertegenwoordigt een stabiel systeem omdat de AOL- enACL-sluitingsgraad 20 dB/decentagebelasting bedraagt.

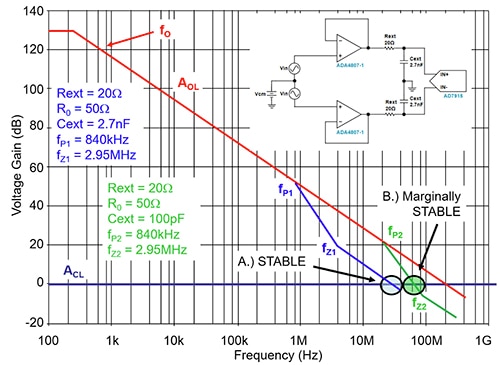

De toevoeging van Rext en Cext en de SAR ADC wijzigt de versterkerkring door het creëren van een systeemnul en -pool (Afbeelding 4). Het systeem bestaat uit een 16-bit, 1 megasample per seconde (MSPS) AD7915 differentiële PulSAR ADC en een 180 MHz, rail-to-rail input/output ADA4807-1 versterker, beide van Analog Devices. De combinatie van de versterker en ADC vereist Rext vanwege de 30 picofarad (pF) (type) ADC ingangscapaciteitsbelasting. Het circuit vereist ook dat Cext als een laadbak fungeert om voldoende lading aan de ADC-ingang te leveren om de ingangsspanning nauwkeurig aan te passen.

Afbeelding 4: Hier wordt de Bode plotrespons van twee ADA4807-opamps weergegeven die de AD7915 SAR ADC met twee afzonderlijke Rext/Cext-paren aansturen. De fP1 en fZ1 hoekfrequenties wijzigen de open loopversterking van de versterker, waardoor een stabiele systeemrespons ontstaat. De fP2- en fZ2-hoekfrequenties wijzigen de open loopversterking van de versterker, waardoor een marginaal stabiele respons ontstaat. (Bron afbeelding: DigiKey)

Afbeelding 4: Hier wordt de Bode plotrespons van twee ADA4807-opamps weergegeven die de AD7915 SAR ADC met twee afzonderlijke Rext/Cext-paren aansturen. De fP1 en fZ1 hoekfrequenties wijzigen de open loopversterking van de versterker, waardoor een stabiele systeemrespons ontstaat. De fP2- en fZ2-hoekfrequenties wijzigen de open loopversterking van de versterker, waardoor een marginaal stabiele respons ontstaat. (Bron afbeelding: DigiKey)

De schakeling in Afbeemdo,g 4 kan potentieel oscilleren als gevolg van de ADC capacitieve belasting en de schakelende lading van de ADC bij de initiële acquisitie. De extra pool en nul die door de uitgangscomponenten van de Rext/Cext-versterker worden gecreëerd, zorgen voor een stabiel systeem, zodat de kruising van de open en gesloten-lusversterkingscurve groter is dan 20 dB/decentiel, wat een fasemarge van minder dan 45° oplevert. Deze configuratie, met fP2 en fZ2, creëert een onstabiel circuit.

Om instabiliteit te voorkomen, moeten ontwerpers bij de evaluatie van de open-loop versterkingscurve van de versterker met Rext en Cext in de schakeling het effect van de open-loop uitgangsweerstand van de versterker,RO, meenemen. De combinatie vanRO gelijk aan 50 ohm (W), Rext en Cext wijzigt de open-loop responscurve door de introductie van één pool (fP, Vergelijking 1) en één nul (fZ, Vergelijking 2). De waardenRO, Rext en Cext bepalen de hoekfrequentie van fP. De waarden van Rext en Cext bepalen de nul-hoekfrequentie, fZ.

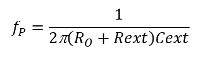

Vergelijking 1

Vergelijking 1

Vergelijking 2

Vergelijking 2

De fP en fZ berekeningen zijn:

fP1 = 842 kHz

fZ1 = 2,95 MHz

met: RO = 50 W

Rext = 20 W

Cext = 2,7 nanofarads (nF)

fP2 = 22,7 MHz

fZ2 = 79,5 MHz

met: RO = 50 W

Rext = 20 W

Cext = 0,1 nF

De bovenstaande waarden voor fP1 en fZ1 zorgen voor een stabiel systeem voor de AD7915 en ADA4807-1.

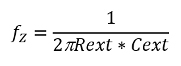

Aansturen met de Easy Drive AD4021 SAR ADC

Een alternatief voor de AD7915 is de AD4021 20-bit 1 MSPS Easy Drive SAR-convertor. De AD4021-apparaatfamilie reduceert de terugslag en de ingangsstroom sterk tot 0,5 microampère (μA)/MSPS. De Easy Drive heeft een lager stroomverbruik en een minder complexe signaalketen.

De analoge ingang van de AD4021 heeft een schakeling die de typische geschakelde condensator SAR-ingang niet-lineaire terugslag van de lading reduceert. De terugslagreductie en een langere acquisitiefase maken het mogelijk om een lagere bandbreedte en lagere power driver versterkers te gebruiken (Afbeelding 5).

Afbeelding 5: Het ingangscircuit en de acquisitietijd van de AD4021 verminderen de terugslag-schakelstroom en ontspannen de strenge eisen van de driver-versterker. (Bron afbeelding: Analog Devices)

Afbeelding 5: Het ingangscircuit en de acquisitietijd van de AD4021 verminderen de terugslag-schakelstroom en ontspannen de strenge eisen van de driver-versterker. (Bron afbeelding: Analog Devices)

De combinatie van terugslagreductie en een langere acquisitietijd maakt ook een grotere Rext-weerstandswaarde in het ingangsweerstands-condensator (RC) filter en een corresponderende kleinere Cext-condensator mogelijk. Deze combinatie van een kleinere Cext-versterkerbelasting verbetert de stabiliteit en verlaagt de vermogensdissipatie.

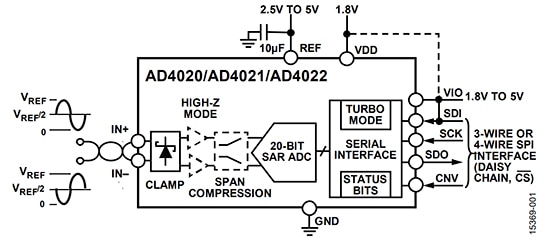

Het aanbevolen aansluitschema voor de AD4021 met een enkele 5 volt voeding lijkt een soortgelijk schema te hebben. De eisen aan de versterker zijn echter versoepeld en de Rext/Cext (R en C) waarden zijn kleiner (Afbeelding 6).

Afbeelding 6: Typisch toepassingsdiagram AD4021 en ADA4807-1, aangedreven door een enkele 5 volt voeding met meer ontspannen versterkervereisten en een grotere Rext-waarde in vergelijking met het aansturen van de eerder besproken AD7915. (Bron afbeelding: Analog Devices)

Afbeelding 6: Typisch toepassingsdiagram AD4021 en ADA4807-1, aangedreven door een enkele 5 volt voeding met meer ontspannen versterkervereisten en een grotere Rext-waarde in vergelijking met het aansturen van de eerder besproken AD7915. (Bron afbeelding: Analog Devices)

In Afbeelding 6 maakt de op SAR gebaseerde AD4021 ook gebruik van een DAC voor de herverdeling van ladingen. De ADC heeft een onboard conversieklok en een seriële klok. Voor het conversieproces is dus geen synchrone klok (SCK) nodig. Deze klokconfiguratie maakt de verlenging van de acquisitietijd mogelijk, wat de nauwkeurigheid verbetert door meer tijd te geven voor het ingangssignaal om tot een definitieve waarde te komen.

De belangrijkste overweging voor de aandrijfversterker voor zowel de AD7915 als de AD4021 is ruis, aangezien de versterker/Rext/Cext combinatie van een full-scale stap naar een 16-bits niveau (0,0015%, 15 ppm) voor de AD7915, en een 20-bits niveau (0,00001%, 1 ppm) voor de AD4021 moet bezinken.

Om de signaal-naar-ruis (SNR) prestaties van de AD7915 en AD4021 te behouden, moet de ruis van de driver-versterker minder dan een derde van de ruis van de ADC zijn. De AD4021 ruis is 60 microvolt rms (mVrms), waardoor de versterker/Rext/Cext combinatie minder dan 20 mVrms moet zijn. De AD4021-ruis is 31,5 mVrms, waardoor de versterker/Rext/Cext-combinatie minder dan 10,5 mVrms moet zijn.

De Precision ADC Driver Tool van Analog Devices helpt ontwerpers snel de juiste Rext- en Cext-waarden te berekenen. Met een geselecteerde driver en ADC modelleert deze tool de insteltijd, de ruis en het vervormingsgedrag van het circuit.

Conclusie

De SAR ADC blijft de ultrasnelle data-acquisitie, industriële besturing en instrumentatietoepassingen domineren. De externe ingangscircuits voor deze apparaten - de aandrijfversterker en het ingangsfilter - moeten echter speciale aandacht krijgen om rekening te houden met mogelijke problemen bij het inschakelen van de lading en de stabiliteit van de versterker.

De oplossing voor een nauwkeurige regeling van het ingangssignaal voor de meeste SAR-convertors, zoals de AD7916 en AD4021, ligt in de op versterker-driver, in dit geval de ADA4807-1. Zoals afgebeeld vormen deze apparaten, ondersteund door de juiste uitgangsweerstands- en condensatorwaarden, een solide basis waarop een uiterst nauwkeurig, robuust, 16-bits of 20-bits SAR-convertorsysteem met hoge resolutie kan worden gebouwd.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.