Waarom en hoe Efinix FPGA's gebruiken voor AI/ML-beeldvorming - Deel 1: Aan de slag

Bijgedragen door De Europese redacteurs van DigiKey

2023-04-20

Notitie van de redactie: Nieuwe benaderingen van FPGA-architecturen zorgen voor een fijnmaziger controle en meer flexibiliteit om tegemoet te komen aan de behoeften van machinaal leren (ML) en kunstmatige intelligentie (AI). Deel 1 van deze tweedelige serie introduceert een dergelijke architectuur van Efinix en hoe ermee aan de slag te gaan met behulp van een ontwikkelbord. Deel 2 bespreekt de interfacing van het ontwikkelingsbord met externe apparaten en randapparatuur, zoals een camera.

FPGA's spelen een cruciale rol in vele toepassingen, van industriële besturing en veiligheid tot robotica, ruimtevaart en automobielindustrie. Dankzij het flexibele karakter van de programmeerbare logische kern en hun ruime interfacemogelijkheden is een groeiend gebruik van FPGA's bij beeldverwerking wanneer ML-inferentie moet worden toegepast. FPGA's zijn ideaal voor het implementeren van oplossingen met verschillende snelle camera-interfaces. Bovendien maken FPGA's ook de implementatie van specifieke verwerkingspijplijnen in de logica mogelijk, waardoor knelpunten die bij CPU- of GPU-gebaseerde oplossingen zouden optreden, worden weggenomen.

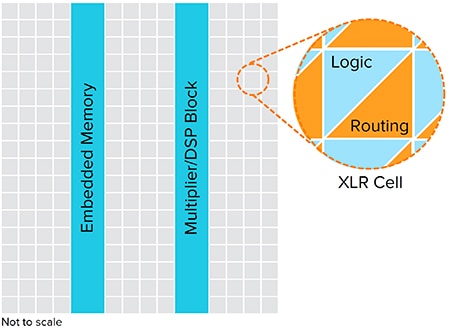

Voor veel ontwikkelaars vereisen hun toepassingen echter meer ML/AI-functionaliteit en fijnmaziger controle of routing en logica, dan wat klassieke FPGA-architecturen met combinatorische logische blokken (CLB's) kunnen bieden. Nieuwere benaderingen van FPGA-architecturen pakken deze problemen aan. De Quantum-architectuur van Efinix gebruikt bijvoorbeeld een eXchangeable Logic and Routing (XLR) blok.

Dit artikel bespreekt de belangrijkste kenmerken en eigenschappen van de Efinix FPGA-architectuur, met de nadruk op de AI/ML-mogelijkheden en een inleiding tot realistische implementaties. Vervolgens wordt een ontwikkelbord en bijbehorende hulpmiddelen besproken die ontwikkelaars kunnen gebruiken om snel aan de slag te gaan met hun volgende AI/ML-beeldvormingsontwerp.

Efinix FPGA-apparaten

Efinix biedt momenteel twee series apparaten aan. Het introduceerde aanvankelijk de Trion-familie, die logische dichtheden biedt van 4000 (4K) tot 120K logische elementen (LE's), en wordt vervaardigd met behulp van een SMIC 40LL-proces. De nieuwste reeks apparaten, de Titanium-familie, biedt logische dichtheden van 35K tot 1 miljoen (1M) logische elementen, en wordt vervaardigd op de zeer populaire TSMC 16 nanometer (nm) node.

Beide aanbiedingen zijn gebaseerd op de Quantum-architectuur, die uniek is in de FPGA-wereld. De standaard FPGA-architectuur is gebaseerd op CLB's die, op het eenvoudigste niveau, een opzoektabel (LUT) en flip-flops bevatten. De CLB's implementeren logische vergelijkingen die vervolgens via routing met elkaar worden verbonden. De Quantum-architectuur van Efinix stapt met het XLR-blok af van afzonderlijke logica- en routingblokken.

Wat een XLR-blok uniek maakt, is dat het kan worden geconfigureerd om te functioneren als een logische cel met een LUT, een register en een adder, of een routeringsmatrix. Deze aanpak biedt een fijnmaziger architectuur die routeringsflexibiliteit biedt, waardoor implementaties die veel logica of veel routering vergen de gewenste prestaties kunnen leveren.

Afbeelding 1: Wat een XLR-blok uniek maakt, is dat het kan worden geconfigureerd om te functioneren als een logische cel met een LUT, een register en een adder, of een routeringsmatrix. (Bron afbeelding: Efinix)

Afbeelding 1: Wat een XLR-blok uniek maakt, is dat het kan worden geconfigureerd om te functioneren als een logische cel met een LUT, een register en een adder, of een routeringsmatrix. (Bron afbeelding: Efinix)

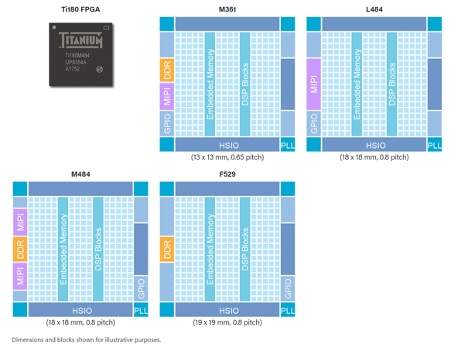

Als nieuwste familie bieden de Titanium-toestellen de meest geavanceerde functies voor de ontwikkelaar (Afbeelding 2). Samen met de XLR-kern bieden zij multi-gigabit seriële verbindingen die werken met 16 gigabits per seconde (Gbps) of 25,8 Gbps, afhankelijk van het gekozen apparaat. Deze multi-gigabitverbindingen zijn van cruciaal belang om een snelle gegevensoverdracht op en van de chip mogelijk te maken.

Afbeelding 2: De Titanium FPGA Ti180 wordt geleverd in verschillende opties, afhankelijk van de busbreedte, I/O en geheugenvereisten. (Bron afbeelding: Efinix)

Afbeelding 2: De Titanium FPGA Ti180 wordt geleverd in verschillende opties, afhankelijk van de busbreedte, I/O en geheugenvereisten. (Bron afbeelding: Efinix)

Titanium-apparaten bieden ook een breed scala aan in-/uitvoer (I/O) interfacemogelijkheden die kunnen worden gegroepeerd als general purpose I/O (GPIO), en die single-ended I/O-standaarden kunnen ondersteunen, zoals laagspannings-CMOS (LVCMOS) bij 3,3 volt, 2,5 volt en 1,8 volt.

Voor snelle en differentiële interfacing bieden de Titanium-apparaten high-speed I/O (HSIO) die single-ended I/O-standaarden ondersteunt zoals LVCMOS bij 1,2 volt, 1,5 volt, en SSTL en HSTL. Differentiële I/O-standaarden die door HSIO worden ondersteund zijn onder meer LVDS (Low Voltage Differential Signaling), differentiële SSTL en HSTL.

Moderne FPGA's vereisen ook nauw gekoppelde geheugens met hoge bandbreedte, die worden gebruikt voor de opslag van beeldframes voor beeldverwerkingstoepassingen, steekproefgegevens voor signaalverwerking, en natuurlijk om besturingssystemen en software te draaien voor processoren die in de FPGA zijn geïmplementeerd. De Titanium-reeks van apparaten biedt de mogelijkheid tot interface met Dynamic Data Rate Four (DDR4) en low-power DDR4(x) (LPDDR4(x)). Afhankelijk van het gekozen Titanium-apparaat is de busbreedte-ondersteuning x32 (J) of x16 (M), terwijl sommige apparaten geen LPDDR4-ondersteuning hebben (L).

Titanium FPGA's zijn gebaseerd op SRAM en hebben een configuratiegeheugen nodig, waarbij de configuratie van het apparaat wordt uitgevoerd via master/slave Serial Peripheral Interconnect (SPI) of JTAG. Om ervoor te zorgen dat deze configuratiemethode veilig is, maakt de Titanium FPGA gebruik van AES GCM-encryptie van de bitstream, samen met AES GCM en RSA-4096 voor bitstreamverificatie. Een dergelijke sterke beveiliging is vereist omdat FPGA's worden ingezet aan de rand, waar kwaadwillenden toegang zouden kunnen krijgen en hun gedrag zouden kunnen manipuleren.

Introductie van het ontwikkelingsbord

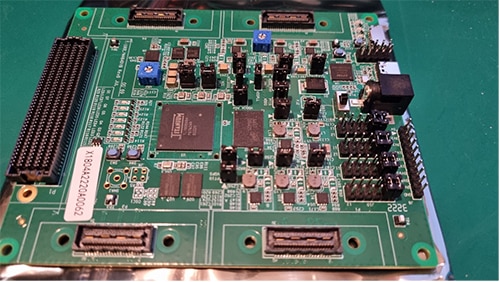

Ontwikkelingskaarten vormen een essentieel onderdeel van het FPGA-evaluatieproces, aangezien zij kunnen worden gebruikt om de mogelijkheden van een apparaat en prototype-toepassingen te onderzoeken, en aldus het algemene risico helpen verminderen. De eerste ontwikkelkaart die beschikbaar is om Titanium FPGA's te evalueren en te beginnen met prototyping-toepassingen is de Ti180 M484 (Afbeelding 3). Het bord heeft een FPGA Mezzanine Card (FMC) connector en vier Samtec QSE-connectors.

Afbeelding 3: Naast een Titanium FPGA beschikt de Ti180 M484-ontwikkelingskit over een FMC-connector en vier Samtec QSE-connectoren. (Bron afbeelding: Adam Taylor)

Afbeelding 3: Naast een Titanium FPGA beschikt de Ti180 M484-ontwikkelingskit over een FMC-connector en vier Samtec QSE-connectoren. (Bron afbeelding: Adam Taylor)

De Ti180 FPGA op dit ontwikkelingsbord biedt 172K XLR-cellen, 32 globale klokken, 640 digitale signaalverwerkingselementen (DSP) en 13 megabits (Mbits) ingebouwd RAM. De DSP-elementen bieden de mogelijkheid om fixed point 18 x 19 vermenigvuldigingen en 48-bit vermenigvuldigingen uit te voeren. Deze DSP kan ook worden geoptimaliseerd voor SIMD-bewerkingen (single instruction, multiple data) in een dubbele of quadconfiguratie. DSP-elementen kunnen ook worden geconfigureerd om drijvende-kommabewerkingen uit te voeren.

Zoals de meeste ontwikkelborden biedt het Ti180-ontwikkelbord eenvoudige LED's en knoppen. De echte kracht zit echter in de interfacemogelijkheden. Het Ti180-ontwikkelingsbord biedt een FMC-connector met een laag aantal pinnen waarmee een groot aantal randapparaten kan worden aangesloten. Omdat het een veel gebruikte standaard is, zijn er veel FMC-kaarten die de interfacing mogelijk maken van snelle analoog-digitaal converter (ADC), digitaal-analoog-convertor (DAC), netwerken en geheugen/opslagoplossingen.

Naast de FMC-aansluiting biedt het bord vier Samtec QSE-connectors waarmee de ontwikkelaar uitbreidingskaarten kan toevoegen. Deze QSE-connectors worden gebruikt voor MIPI-ingangen en -uitgangen, waarbij elke QSE-connector een MIPI-ingang of -uitgang biedt.

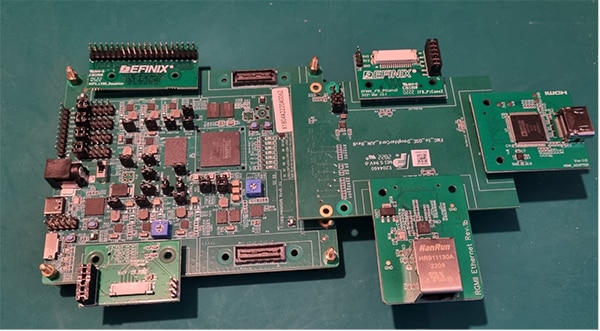

Afbeelding 4: De Ti180 M484-ontwikkelingskit wordt getoond met zijn veelzijdige reeks uitbreidingsopties op basis van QSE- en FMC-connectors. (Bron afbeelding: Adam Taylor)

Afbeelding 4: De Ti180 M484-ontwikkelingskit wordt getoond met zijn veelzijdige reeks uitbreidingsopties op basis van QSE- en FMC-connectors. (Bron afbeelding: Adam Taylor)

Het Ti180-bord biedt ook 256 Mbits LPDDR4 ter ondersteuning van het krachtige geheugen dat nodig is in beeld- of signaalverwerkingstoepassingen. Bovendien biedt de ontwikkelingskaart een reeks klokopties op 25, 33,33, 50 en 74,25 megahertz (MHz), die kunnen worden gebruikt met de phase lock loop (PLL) van het apparaat om verschillende interne frequenties te genereren.

De mogelijkheid om live op het bord te herprogrammeren en debuggen tijdens de ontwikkeling is van cruciaal belang en vereist een JTAG-verbinding, die aan boord wordt geleverd via een USB-C-interface. Er is ook niet-vluchtig geheugen in de vorm van twee NOR-flashapparaten van 256 Mbit die kunnen worden gebruikt om de configuratieoplossing te demonstreren.

Het bord wordt gevoed door een universele voedingsadapter van 12 volt die in de doos is bijgesloten. Ook inbegrepen is een FMC-to-QSE-breakout, samen met QSE-gebaseerde uitbreidingskaarten voor HDMI, Ethernet, MIPI en LVDS. Om de beeldverwerkingsmogelijkheden van Ti180 te demonstreren, worden ook een dubbele RPI-dochterkaart en twee IMX477-camerakaarten meegeleverd.

De softwareomgeving

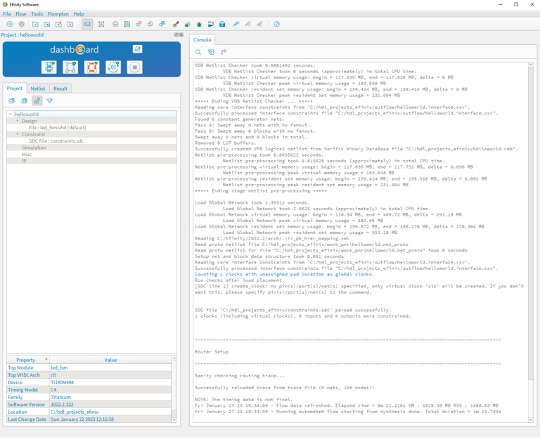

Voor de implementatie van ontwerpen die gericht zijn op het Ti180-ontwikkelbord wordt de Efinix-software Efinity gebruikt. De software maakt het mogelijk een bitstroom te genereren via synthese en place and route. Het biedt ontwikkelaars ook intellectueel eigendom (IP) blokken, timing analyse en on-chip debugging.

Merk op dat een ontwikkelbord nodig is om toegang te krijgen tot de Efinity-software. In tegenstelling tot andere verkopers heeft de tool echter geen verschillende versies waarvoor extra licenties nodig zijn.

Binnen Efinity worden nieuwe projecten gemaakt die gericht zijn op het geselecteerde apparaat. RTL-bestanden kunnen dan worden toegevoegd aan het project, en er kunnen beperkingen worden gemaakt voor timing en I/O-ontwerp. Binnen Efinity kunnen ontwikkelaars ook het I/O-ontwerp implementeren, met gebruikmaking van de HSIO, GPIO en gespecialiseerde I/O.

Afbeelding 5: Binnen Efinity worden nieuwe projecten gemaakt die gericht zijn op het geselecteerde apparaat. (Bron afbeelding: Adam Taylor)

Afbeelding 5: Binnen Efinity worden nieuwe projecten gemaakt die gericht zijn op het geselecteerde apparaat. (Bron afbeelding: Adam Taylor)

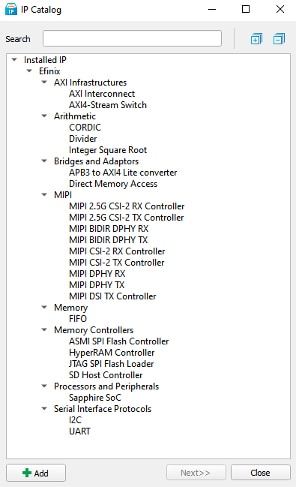

Een cruciaal element van FPGA-ontwerp is het gebruik van IP, vooral voor complexe IP zoals AXI-interconnecties, geheugencontrollers en softcore-processoren. Efinity biedt ontwikkelaars een reeks IP-blokken die kunnen worden gebruikt om het ontwerpproces te versnellen.

Afbeelding 6: Efinity biedt ontwikkelaars een IP-catalogus die zij kunnen gebruiken om het ontwerpproces te versnellen. (Bron afbeelding: Adam Taylor)

Afbeelding 6: Efinity biedt ontwikkelaars een IP-catalogus die zij kunnen gebruiken om het ontwerpproces te versnellen. (Bron afbeelding: Adam Taylor)

Hoewel FPGA's uitstekend geschikt zijn voor de implementatie van parallelle verwerkingsstructuren, bevatten veel FPGA-ontwerpen softcore processoren. Deze bieden de mogelijkheid tot sequentiële verwerking, zoals netwerkcommunicatie. Om de inzet van de softcore processors in de Efinix apparaten mogelijk te maken, levert Efinity de Sapphire system-on-chip (SoC) configuratietool. Met Sapphire kan de ontwikkelaar een multiprocessorsysteem definiëren dat zowel caches als cachecoherentie heeft over meerdere processoren, samen met de mogelijkheid om een ingebed Linux-besturingssysteem te draaien. Binnen Sapphire kan de ontwikkelaar kiezen tussen één en vier softcore processors.

De softcore-processor die wordt geïmplementeerd is de VexRiscV soft CPU, die gebaseerd is op de RISC-V instructieset-architectuur. De VexRiscV-processor is een 32-bits implementatie met uitbreidingen voor pipelining en een configureerbare functieset, waardoor hij ideaal is voor implementatie in Efinix-apparaten. Optionele configuraties omvatten een vermenigvuldiger, atomaire instructies, uitbreidingen voor drijvende komma en gecomprimeerde instructies. Afhankelijk van de configuratie van het SoC-systeem liggen de prestaties tussen 0,86 en 1,05 DMIPS/MHz.

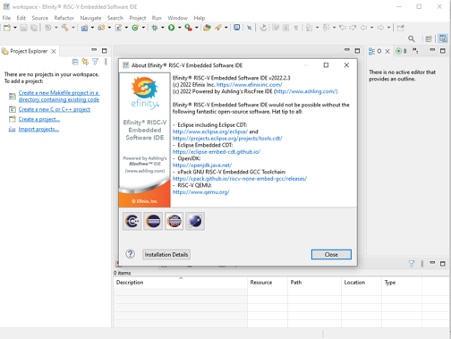

Zodra de hardwareomgeving is ontworpen en geïmplementeerd in het Efinix-apparaat, kan de toepassingssoftware worden ontwikkeld met behulp van de Ashling RiscFree IDE. Ashling RiscFree is een op Eclipse gebaseerde IDE die de creatie en compilatie van toepassingssoftware mogelijk maakt, samen met debugging op het doel om de toepassing te verfijnen vóór de implementatie.

Afbeelding 7: Ashling RiscFree is een op Eclipse gebaseerde IDE die de creatie en compilatie van toepassingssoftware mogelijk maakt, samen met debugging op het doel. (Bron afbeelding: Adam Taylor)

Afbeelding 7: Ashling RiscFree is een op Eclipse gebaseerde IDE die de creatie en compilatie van toepassingssoftware mogelijk maakt, samen met debugging op het doel. (Bron afbeelding: Adam Taylor)

Als een embedded Linux oplossing wordt ontwikkeld, worden alle noodzakelijke bootartefacten geleverd, inclusief First Stage Boot Loader, OpenSBI, U-Boot en Linux met Buildroot. Als alternatief kan de ontwikkelaar FreeRTOS gebruiken als een real-time oplossing nodig is.

AI-implementatie

De AI-implementatie van Efinix bouwt voort op de RISC-V softcore-operatie. Dit maakt gebruik van de aangepaste instructiemogelijkheden van de RISC-V-processor om de versnelling van TensorFlow Lite-oplossingen mogelijk te maken. Door het gebruik van de RISC-V-processor kunnen gebruikers ook aangepaste instructies maken die kunnen worden gebruikt als onderdeel van de voor- of nabewerking na de AI-inferentie, waardoor een meer responsieve en deterministische oplossing ontstaat.

Om te beginnen met een AI-implementatie is de eerste stap het verkennen van de Efinix-modelzoo, een bibliotheek van AI/ML-modellen die geoptimaliseerd zijn voor de eindtechnologie. Voor ontwikkelaars die met de Efinix-apparaten werken, is de modeldierentuin toegankelijk en kan het netwerk worden getraind met behulp van Jupyter Notebooks of Google Colab. Zodra het netwerk is getraind, kan het worden omgezet van een floating point model naar een gekwantificeerd model met behulp van de TensorFlow Lite-convertor.

Eenmaal in het TensorFlow Lite-formaat kan de tinyML versneller van Efinix worden gebruikt om een inzetbare oplossing op de RISC-V-oplossing te creëren. Met de tinyML-generator kan de ontwikkelaar de implementatie van de versneller aanpassen en de projectbestanden genereren. Wanneer het op deze manier wordt ingezet, kan de versnelling variëren van 4x tot 200x, afhankelijk van de gekozen architectuur en aanpassingen.

Conclusie

Efinix-apparaten bieden ontwikkelaars flexibiliteit dankzij hun unieke XLR-architectuur. De toolchain biedt de mogelijkheid om niet alleen RTL-ontwerpen te implementeren, maar ook complexe SoC-oplossingen die softcore RISC-V-processors inzetten. Bovenop de softcore SoC is een AI/ML-oplossing gebouwd die de inzet van ML-inferentie mogelijk maakt.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.