FPGA's in de wereld van Arduino: de Snō-module van Alorium gebruiken voor zowel voorgeconfigureerde als aangepaste IP

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2019-05-01

Field-programmable gate arrays (FPGA's) bieden een mogelijke oplossing voor problemen die zich in real-time embedded ontwerpen voordoen met de hardware wanneer de firmware, die op een microcontroller of microprocessor draait, te traag blijkt te zijn. Ze geven ook flexibiliteit ten aanzien van de randapparatuur. FPGA's gebruiken betekent nieuwe programmeertalen (meestal Verilog of VHDL) leren, alsmede een hele nieuwe ontwikkel-workflow om FPGA-bitstreams te genereren en wellicht een hoop geld uitgeven voor een FPGA-ontwikkelbord.

Vanwege deze obstakels zijn veel ontwerpers terughoudend om FPGA's te gaan gebruiken, terwijl deze toch een bijzonder nuttig ontwerphulpmiddel zouden kunnen zijn. Om deze terughoudendheid weg te nemen, werken sommige leveranciers er hard aan om de FPGA-leercurve korter te maken. Arduino heeft bijvoorbeeld het Arduino ABX00022 MKR Vidor 4000 FPGA-ontwikkelingsbord op de markt gebracht (zie “Snel en gemakkelijk FPGA's toepassen met Arduino MKR Vidor 4000”). Arduino MKR Vidor 4000 biedt een nieuwe manier voor het programmeren van FPGA's, die naadloos is geïntegreerd met de uitermate populaire geïntegreerde ontwikkelingsomgeving (integrated development environment - (IDE) van Arduino en zorgt tegelijkertijd voor prestaties op FPGA-niveau door gebruik van speciale Arduino bibliotheek-extensies.

Er is nu een nieuw alternatief voor de tot dusver aangeboden producten, waaronder het Arduino MKR Vidor 4000-bord. Alorium Technology heeft een net iets andere manier ontwikkeld om FPGA's aan de wereld van de embedded-ontwikkeling van Arduino toe te voegen. De benadering van Alorium is zowel geschikt voor voorgeconfigureerde IP-blokken voor I/O-acceleratie als voor aangepaste ontwerpen van IP-blokken.

In dit artikel gaan we eerst kort in op traditionele manieren om FPGA's te gebruiken. Vervolgens wordt dieper ingegaan op de Arduino-compatibele XLR8R22M08V5U0DI en Snō SNOR20M16V3 FPGA-modules van Alorium. Het artikel laat zien hoe Alorium zijn eigen draai heeft gegeven aan het gebruik van FPGA's in het Arduino-continuüm, zowel voor het gebruik van vooraf geconfigureerde IP als voor het maken van een aangepaste IP. Ook wordt uitgelegd hoe ontwerpers kunnen beginnen met het toepassen van de FPGA-modules.

Hoe maak je een Arduino sneller

Honderdduizenden ontwerpers, ingenieurs, ontwikkelaars, doe-het-zelvers en makers over de hele wereld gebruiken nu verschillende versies van de Arduino-ontwikkelingsborden voor de ontwikkeling van embedded systemen voor een breed scala aan toepassingen. De Arduino-borden en Arduino IDE zijn zo populair geworden omdat ze bijzonder eenvoudig te gebruiken en te programmeren zijn.

Aangezien Arduino-gebruikers de originele Arduino-architectuur voor steeds complexere applicaties probeerden te gebruiken, stuitten ze onvermijdelijk op problemen ten aanzien van de prestaties. Een van die problemen was de eenvoudige 8-bits architectuur van de originele Arduino-microcontroller. Een ander probleem was de manier waarop het Arduino-softwaresysteem veel real-time randapparaten implementeert, met behulp van software, terwijl de embedded microcontroller van Arduino geen equivalent hardwareblok heeft.

Een manier om dit probleem aan te pakken, is gebruik te maken van krachtigere microcontrollers, maar het blijft een feit dat software maar weinig kan uithalen in een real-time omgeving. Sommige hoge-snelheid real-time randapparaten moeten simpelweg in hardware worden geïmplementeerd. Het is ook mogelijk om microcontrollers met meer hardware-randapparatuur te gebruiken, maar de juiste mix van randapparatuur varieert van project tot project.

Fabrikanten van microcontrollers zijn op de behoefte aan verschillende randapparatuurmixen ingesprongen door tientallen of soms zelfs honderden variaties binnen één microprocessorfamilie aan te bieden. Dit is vanwege de noodzaak tot bordconnectors met voldoende I/O-pennen om aan alle behoeften te voldoen echter geen haalbare aanpak voor producten op bordniveau zoals de Arduino. Alhoewel er nu vele varianten van het Arduino-bord bestaan, zijn er nog steeds niet genoeg om aan de vereisten van ieder embedded project te voldoen.

FPGA's komen tegemoet aan de behoefte aan variatie in de mix van randapparatuur

Door programmeerbare hardware beschikbaar te maken voor de ontwerper van embedded systemen, kunnen FPGA's voldoen aan de behoefte aan mixen van randapparatuur die van project tot project variëren. Een manier om FPGA-functionaliteit aan een embedded microcontroller-bord toe te voegen, is door eenvoudig een FPGA op te nemen in een bestaand ontwerp. Dat is de benadering waar Arduino zelf voor heeft gekozen bij het ontwerpen van het Arduino MKR Vidor 4000-bord. Het bord combineert de 32-bits Arm® Cortex®-M0+-gebaseerde ATSAMD21G18A-AUT SAMD21 low-power microcontroller van Microchip Technology met de 10CL016YU484C6G Cyclone 10 FPGA van Intel.

Arduino heeft specifiek voor het MKR Vidor 4000-bord diverse hardware-IP-blokken aan de Arduino IDE toegevoegd. Deze randapparatuur is beschikbaar via twee bibliotheken: VidorPeripherals en VidorGraphics. Deze hardware-IP-blokken worden automatisch in de Intel Cyclone 10 FPGA op de Arduino MKR Vidor 4000 geconstrueerd wanneer de relevante randapparatuurbibliotheek wordt opgenomen in een sketch —de naam die Arduino gebruikt voor een programma of code-eenheid. Het huidige aanbod van perifere IP-blokken omvat:

- I2C-poorten

- SPI-poorten

- UART's

- Hoogfrequente PWM-controllers

- Hoge-snelheid timers

- Hoge-snelheid kwadratuurdecoders

- Adafruit Industries Neopixel adresseerbare RGB smart LED-controller

Sommige van deze randapparaten, zoals I2C en SPI, waren al beschikbaar als software-IP-blokken voor vroegere Arduino-borden. Het verschil tussen deze eerdere software-implementaties en de equivalente IP-blokken die geïmplementeerd worden op de FPGA van het Arduino MKR Vidor 4000-bord, is dat de FPGA-versies van deze randapparaten veel betere prestaties leveren. Elke I2C- en SPI-instantiatie wordt bijvoorbeeld met afzonderlijke programmeerbare hardwareblokken in de FPGA van het bord geïmplementeerd. Daardoor is er geen prestatieverlies bij het instantiëren van meerdere van dergelijke seriële poorten.

Door perifere blokken als FPGA-hardware te implementeren en deze beschikbaar te stellen met behulp van hetzelfde bibliotheekmechanisme waar schrijvers van Arduino-sketches al bekend mee zijn, kan het Arduino MKR Vidor 4000-bord het gebruik van FPGA's vergemakkelijken. Het is niet nodig om een nieuwe hardware-beschrijvingstaal (hardware description language - HDL) zoals VHDL of Verilog te leren. Vanuit het oogpunt van de programmeur ziet op FPGA gebaseerde randapparatuur er in feite uit als elk ander C ++ -object. Arduino is van plan om in de toekomst meer van dergelijke hardware IP-blokrandapparatuur toe te voegen.

Het Arduino MKR Vidor 4000-bord is nog geen general-purpose FPGA-ontwikkelingsbord omdat er nog geen ondersteuning is voor directe programmering van de Cyclone 10 FPGA op het bord met behulp van de HDL-code. Arduino is van plan om gevorderde gebruikers de mogelijkheid te bieden meer functionaliteit uit de FPGA van de Arduino MKR Vidor 4000-kaart te halen met behulp van het Quartus HDL-ontwikkelingstool van Intel voor de FPGA's van het bedrijf.

Alorium zet de volgende stap

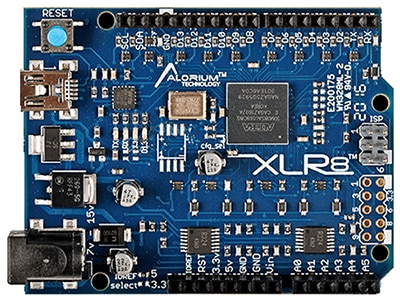

Alorium heeft die stap al gezet met zijn OpenXLR8-methodologie en Xcelerator-blokken (XB's) voor de XLR8R22M08V5U0DI en SNOR20M16V3 Snō FPGA-ontwikkelingsborden die compatibel zijn met Arduino (respectievelijk Afbeelding 1 en Afbeelding 2). Beide borden zijn gebaseerd op verschillende versies van de Intel MAX 10 FPGA-familie met geïntegreerd geheugen met flash-configuratie. De XLR8 combineert de 10M08SAU169C8G MAX 10 van Intel met een 8-bits ATmega328 instructieset-compatibele microcontroller. Deze gebruikt dezelfde vormfactor als de originele Arduino Uno-ontwikkelingsborden en is dus compatibel met de vele schermen en accessoires van Arduino.

Afbeelding 1: het XLR8R22M08V5U0DI-ontwikkelingsbord van Alorium Technology combineert een Intel MAX 10 FPGA met een 8-bits ATmega328 instructieset-compatibele microcontroller, alles in een Arduino Uno-vormfactor. (Bron afbeelding: Alorium Technology)

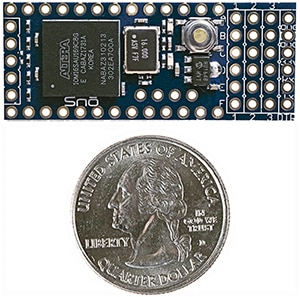

De Snō FPGA-module van Alorium is een veel kleiner ontwikkelingsbord, van slechts 18 x 18 mm, zie Afbeelding 2. Alhoewel het Snō FPGA-ontwikkelingsbord fysiek kleiner is, integreert hij een grotere versie van de Intel MAX 10 FPGA met twee keer zoveel logische elementen: 16K in een 10M16SAU169C8G MAX 10 FPGA tegen 8K in de 10M08 op het XLR8-bord. Hij heeft ook meer dan twee keer zoveel I/O-pennen (32 tegen 14 voor he XLR8 board).

Afbeelding 2: net als het XLR8-ontwikkelingsbord, combineert het Snō FPGA-ontwikkelingsbord van Alorium Technology een 8-bits ATmega328 instructieset-compatibele microcontroller met een Intel MAX 10—in dit geval de 10M16SAU169C8G FPGA. Het Snō FPGA-ontwikkelingsbord is echter veel kleiner. (Bron afbeelding: Alorium Technology)

Alorium biedt ook het SNOMAKRR10-breakout-board dat een Snō FPGA-module accepteert en deze transformeert in een lichtelijk overmaats Arduino vormfactorbord met een USB-poort en aanvullende I/O-pennen voor break-out vanaf de FPGA. Sommige pennen van de Snō FPGA-module zijn naar de Arduino-compatibele schermstiftlijsten van het SnōMAKR breakout-board gerouteerd, terwijl andere naar een aanvullende stiftlijst aan de rand van het bord , tegenover de USB-connector gerouteerd zijn (Afbeelding 3).

Afbeelding 3: het SNOMAKRR10 breakout-board van Alorium converteert het Snō FPGA-ontwikkelingsbord van het bedrijf naar een Arduino-compatibele vormfactor met een USB-poort en een regelaar op het bord, zodat het ontwikkelingsbord direct vanaf de USB-kabel kan worden gevoed. (Bron afbeelding: Alorium Technology)

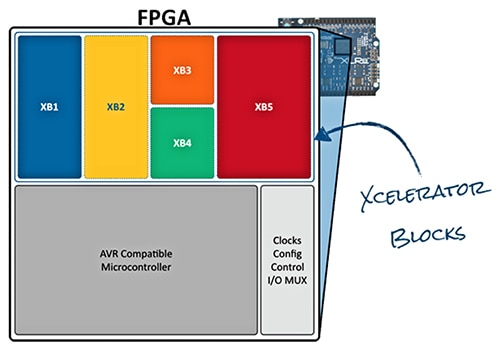

Zowel het XLR8- als het Snō FPGA-ontwikkelingsbord implementeert de 8-bits microcontroller en diens hardware-randapparatuur in één chip—een Intel MAX 10 FPGA. Afbeelding 4 laat zien hoe dit wordt gedaan.

Afbeelding 4: zowel het XLR8 als het Snō FPGA-ontwikkelingsbord implementeert de Atmel AVR-compatibele microcontroller als een soft-core in de MAX 10 FPGA. (Bron afbeelding: Alorium Technology)

De AVR-compatibele microcontrollerkern (linksonder op Afbeelding 4) is dezelfde Atmel ATmega328 8-bits AVR-microcontroller als die in de originele Arduino-ontwikkelingsborden werd gebruikt. De versie van Alorium van de AVR-microcontroller zit echter niet op een aparte chip, maar is als een soft-core in de FPGA geïmplementeerd.

Op Afbeelding 4 zijn vijf XB's van Alorium (XB1 tot XB5) boven de microcontrollerkern te zien. XB's zijn IP-blokken die zijn geïmplementeerd met behulp van de chip-resources van de FPGA. De AVR-microcontroller communiceert met de XB's op de chip via een adresseerbare registerinterface. De XLR8- en Snō-ontwikkelingsborden worden afgeleverd met voorgeïnstalleerde XB's (ook beschikbaar op GitHub) die zijn afgestemd op perifere functies die Arduino-ontwikkelaars vaak nodig hebben, waaronder:

- Kwadratuur-decodering

- Servomotorregeling

- NeoPixel RGB LED regeling

- Enhanced 12-bits ADC

- Floating-point rekenen

Merk op dat de laatste XB op bovenstaande lijst geen echt I/O-randapparatuurblok is; het is een floating-point rekenaccelerator. XB's kunnen elk type hardware-accelerator zijn. Deze zijn niet beperkt tot I/O.

Neem een blok, een willekeurig blok

Zowel de XLR8- als de Snō FPGA-ontwikkelingsborden kunnen in het veld updates ondergaan door verschillende XB's te selecteren (of meerdere kopieën van dezelfde XB) om in de FPGA te worden geïnstantieerd met behulp van de OpenXLR8 ontwikkel-workflow van Alorium. Ontwikkelaars kunnen ook persoonlijk aangepaste Xcelerator-blokken creëren door OpenXLR8 flow van Alorium te gebruiken (Afbeelding 5).

Afbeelding 5: OpenXLR8 ontwikkel-workflow van Alorium laat ontwerpers nieuwe hardwareblokken creëren (met behulp van Quartus Prime ontwerptools van Intel) en deze aan de Arduino IDE toevoegen. (Bron afbeelding: Alorium Technology)

Het creëren van een aangepaste XB vereist momenteel kennis van de hardware-beschrijvingstaal Verilog of VHDL en bekendheid met de Intel Quartus FPGA toolsuite—met name versie 17.1 van de Quartus Prime Lite Edition en ModelSim-simulatietools van Mentor Graphics. Voor FPGA-ontwikkeling zijn HDL's nodig omdat deze de ontwerper de mogelijkheid bieden om parallelle uitvoering van meerdere taken op een welomschreven, standaard manier uit te drukken. Talen van hoog niveau (high level languages - HLL's) zoals C en C++ zijn inherent sequentiële talen.

HLL-compilers nemen de HLL-broncode en vertalen deze in lange sequensen van machine-instructies, die meestal een voor een worden uitgevoerd. Dat is de reden waarom FPGA's zoveel sneller zijn dan processors — FPGA's kunnen duizenden simultane taken uitvoeren, als de FPGA maar groot genoeg is. Er zijn HLL-compilers die in C of C++ geschreven code in een HDL kunnen vertalen, die vervolgens wordt verwerkt door conventionele FPGA-tools, maar deze HLL-compilers maken op dit moment nog geen deel uit van de OpenXLR8 ontwerp-workflow van Alorium.

Zodra een XB echter is ontworpen en aan debugging onderworpen met behulp van HDL- en FPGA-ontwikkeltools, kan het in de Arduino IDE worden gebruikt zoals elk ander Arduino-bibliotheekblok. Alorium is momenteel ook bezig met het ontwikkelen van aanvullende XB's voor de Arduino IDE-bibliotheken.

Conclusie

Bij het creëren van hun FPGA-ontwikkelborden, erkennen zowel Arduino als Alorium Technology de groeiende behoefte van ontwerpers aan meer embedded functionaliteit van deze goedkope ontwikkelingsborden. Hoewel de twee bedrijven ietwat verschillende paden hebben bewandeld, zijn ze allebei op weg naar hetzelfde einddoel: een manier vinden om FPGA's toegankelijker te maken voor meer embedded-ontwikkelaars. Op het eenvoudigste niveau brengen zowel de benadering van Arduino als die van Alorium hardware-design terug tot iets dat niet moeilijker is dan het kiezen van blokken en het uitvoeren van scripts.

Op dit moment is de volledige ontwerp-workflow nog niet zo eenvoudig geworden als mogelijk zou zijn. Arduino heeft zijn volledige FPGA ontwikkel-workflow nog niet opengesteld voor HDL-ontwikkelaars. De ontwerp-workflow van Alorium omvat geen HDL-ontwerp, maar vereist kennis van Verilog of VHSL FPGA ontwerptalen en -tools.

Deze producten hebben de deur echter op een kier gezet, dus het is op zijn minst theoretisch mogelijk om te profiteren van andere stappen vooruit in de ontwikkeling van FPGA, zoals C en C ++ hardware-compilers. Tot die tijd is het, met behulp van de eenvoudige methoden die Alorium Technology en Arduino hebben ontwikkeld om deze mogelijkheden aan Arduino IDE toe te voegen, toch mogelijk om iets van de prestaties van de FPGA mee te pikken.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.