Ontwerpen en certificeren van veilige weerstandstemperatuurdetectorsystemen (RTD)

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2023-07-24

Weerstandstemperatuurdetectors (RTD's), bestaande uit een transducer en een analoog front-end (AFE) signaalconditioneringscircuit, worden veel gebruikt, en zijn nauwkeurig en betrouwbaar. Voor missiekritische en zeer betrouwbare toepassingen is het echter vaak nodig om een functioneel veilig systeem te ontwerpen en te garanderen via het Route 1S- of Route 2S-onderdeelcertificeringsproces.

Het certificeren van een systeem voor functionele veiligheid is een complex proces, omdat alle componenten in het systeem moeten worden beoordeeld op mogelijke storingsmodi en -mechanismen. Er zijn verschillende methoden om storingen vast te stellen. Het gebruik van onderdelen die al gecertificeerd zijn, helpt hierbij en vereenvoudigt het certificeringsproces.

Merk op dat ‘betrouwbaarheid’ gerelateerd is aan ‘functioneel veilig’, maar niet hetzelfde is. Simpel gezegd, verwijst ‘betrouwbaar’ naar een ontwerp en implementatie die werken volgens de specificaties zonder problemen of storingen, terwijl ‘functioneel veilig’ betekent dat eventuele storingen door het ontwerp moeten worden gedetecteerd. Voor kritieke toepassingen zijn zowel betrouwbaarheid als functionele veiligheid nodig.

Dit artikel behandelt de basisprincipes van RTD's en hun signaalconditioneringscircuits met het oog op functioneel veilige certificering. Daarnaast worden de verschillende niveaus van betrouwbaarheid en ‘failure certification’ besproken, en wat er nodig is om hieraan te voldoen via beide routes. Twee meerkanaals RTD AFE IC's, het AD7124 paar van Analog Devices, samen met een bijbehorend evaluatieboard, worden gebruikt om de belangrijkste punten te illustreren.

De rol van functionele veiligheid

De rol van functionele veiligheid is het afwezig zijn van onaanvaardbaar risico van letsel of schade met betrekking tot de gezondheid van de mens, door de juiste implementatie van een of meer automatische beschermings-/veiligheidsfuncties. Hierbij wordt gezorgd dat het product, apparaat of systeem veilig blijft functioneren als er een storing optreedt. Dit is nodig in een breed scala aan industriële, commerciële en zelfs sommige consumententoepassingen, zoals:

- Autonome voertuigen

- Machineveiligheid en robotica

- Industriële besturingssystemen (ICS)

- Consumentenproducten voor smart homes

- Slimme fabrieken en toeleveringsketens

- Systemen met veiligheidsinstrumenten en regelsystemen voor gevaarlijke locaties

In een functioneel veilig ontwerp is de functie van een hoofdschakelaar bijvoorbeeld nog steeds het uitschakelen van de stroom, zelfs als andere componenten in het systeem falen (afbeelding 1).

Afbeelding 1: In een functioneel veilig systeem kan er geen twijfel bestaan dat deze schakelaar doet waarvoor hij ontworpen is. (Bron afbeelding: Pilla via City Electric Supply Co.)

Afbeelding 1: In een functioneel veilig systeem kan er geen twijfel bestaan dat deze schakelaar doet waarvoor hij ontworpen is. (Bron afbeelding: Pilla via City Electric Supply Co.)

Basisprincipes van RTD

Waarom is temperatuur belangrijk voor functionele veiligheid? Een reden hiervoor is dat temperatuur de meest gemeten fysieke parameter is. Dit heeft vaak te maken met veiligheids- of kritische toepassingen en wordt ondersteund door een brede selectie transducers. Hieronder vallen RTD's, die conceptueel eenvoudig zijn: ze maken gebruik van de bekende en herhaalbare temperatuurweerstandscoëfficiënt (TCR) van metalen zoals nikkel, koper en platina. Platina RTD's met een weerstand van 100 ohm (Ω) en 1000 Ω bij 0 °C worden het meest gebruikt en zijn geschikt voor het bereik van -200 °C tot +850 °C.

Deze RTD's hebben een zeer lineaire weerstand-temperatuurverhouding over dit temperatuurbereik. Voor situaties met een zeer hoge nauwkeurigheid zijn er correctie- en compensatietabellen en -factoren die kunnen worden toegepast. De platina RTD met een nominale weerstand van 100 Ω (aangeduid als PT100) heeft een typische weerstand van 18 Ω bij -200 °C en 390,4 Ω bij +850 °C.

Het gebruik van een RTD vereist dat deze wordt bekrachtigd met een bekende stroom die meestal wordt beperkt tot ongeveer 1 milliampère (mA) om zelfopwarming te minimaliseren. Andere stroomwaarden worden ook gebruikt, afhankelijk van de nominale weerstand van de RTD.

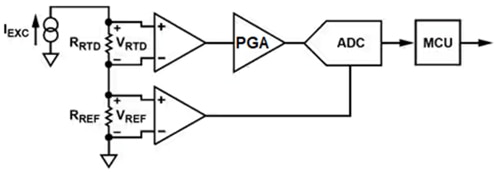

De spanningsval over de RTD wordt tegelijkertijd gemeten via een AFE, bestaande uit een programmeerbare versterker (PGA) en in bijna alle gevallen een analoog-digitaalomzetter (ADC) in combinatie met een microcontroller (MCU) (afbeelding 2).

Afbeelding 2: Een RTD die wordt gebruikt om temperatuur te meten, vereist het sturen van een bekende stroom door de RTD en het meten van de spanningsval, waarna de wet van Ohm wordt toegepast. (Bron afbeelding: Digi-Key)

Afbeelding 2: Een RTD die wordt gebruikt om temperatuur te meten, vereist het sturen van een bekende stroom door de RTD en het meten van de spanningsval, waarna de wet van Ohm wordt toegepast. (Bron afbeelding: Digi-Key)

De schakeltopologie van dit basisschema is identiek aan het gebruik van een meetweerstand om de stroom door een belasting te bepalen, maar hier worden de bekende en onbekende variabelen omgewisseld. Voor stroomdetectie is de weerstand bekend terwijl de stroom onbekend is, dus de berekening is I = V/R. Voor RTD's is de stroom bekend, maar de weerstand niet, dus de berekening is R = V/I.

De PGA is nodig om de signaalintegriteit te behouden en het dynamische bereik te maximaliseren, aangezien de spanningsniveaus over de RTD kunnen variëren van tientallen millivolts tot honderden millivolts, afhankelijk van het RTD-type en de temperatuur.

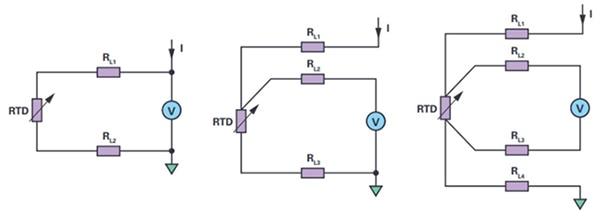

De fysieke verbinding tussen de bekrachtigingsbron, de RTD en de PGA kan een twee-, drie- of vierdraads interface zijn. Hoewel twee afleidingen in principe voldoende zijn, zijn er problemen met IR-daling in de verbindingsdraden evenals andere artefacten. Het gebruik van de drie- en vierdraads topologieën in een meer geavanceerde Kelvin-verbinding resulteert in nauwkeurigere en consistentere prestaties, ook al brengt dit extra bedradingskosten met zich mee (afbeelding 3).

Afbeelding 3: De RTD kan worden aangestuurd en gemeten via slechts twee draden (links), maar het gebruik van drie draden (midden) en zelfs vier draden (rechts, Kelvin-aansluiting) maakt het mogelijk om verschillende storingsbronnen als gevolg van de draden te elimineren. (Bron afbeelding: Analog Devices)

Afbeelding 3: De RTD kan worden aangestuurd en gemeten via slechts twee draden (links), maar het gebruik van drie draden (midden) en zelfs vier draden (rechts, Kelvin-aansluiting) maakt het mogelijk om verschillende storingsbronnen als gevolg van de draden te elimineren. (Bron afbeelding: Analog Devices)

Begin met terminologie en normen

Zoals bij veel specialismen het geval is, kent functionele veiligheid veel unieke termen, datasets en acroniemen die veel worden gebruikt in gerelateerde besprekingen. Denk hierbij aan:

- Failures in time (FIT): het aantal storingen dat kan worden verwacht als het apparaat een miljard (109) uur in bedrijf is.

- Failure modes and effects analysis (FMEA): het proces waarbij zoveel mogelijk componenten, samenstellingen en subsystemen worden bekeken om mogelijke storingsmodi in een systeem en bijbehorende oorzaken en gevolgen te identificeren.

- Failure modes effects and diagnostic analyses (FMEDA): een systematische analysetechniek om uitvalpercentages, storingsmodi en diagnostische mogelijkheden op subsysteem-/productniveau te bepalen.

Voor een volledige analyse zijn FIT-gegevens nodig samen met FMEDA's voor de verschillende onderdelen in het systeem. FMEA biedt alleen kwalitatieve informatie, terwijl FMEDA zowel kwalitatieve als kwantitatieve informatie biedt, waardoor gebruikers een mate van belangrijkheid op storingsmodi kunnen meten en deze naar belangrijkheid kunnen rangschikken. FMEDA voegt informatie toe over risico's, storingsmodi, effecten en diagnostiek, en betrouwbaarheid.

- Safety Integrity Level (SIL): er zijn vier verschillende integriteitsniveaus verbonden aan SIL: SIL 1, SIL 2, SIL 3 en SIL 4. Hoe hoger het SIL-niveau, hoe hoger het bijbehorende veiligheidsniveau en hoe kleiner de kans dat een systeem niet naar behoren functioneert.

Een SIL 2-classificatie geeft aan dat meer dan 90% van de storingen binnen het systeem gediagnosticeerd kunnen worden. Om een ontwerp te certificeren, moet de systeemontwerper bewijs overleggen aan het certificeringsbureau over de potentiële storingen, of dit veilige storingen of gevaarlijke storingen zijn en hoe de storingen kunnen worden gediagnosticeerd.

- IEC 61508, formeel getiteld "Functionele veiligheid van elektrische/elektronische/programmeerbare elektronische systemen verbandhoudend met veiligheid" (en informeel gewoon "Elektronische functionele veiligheid" genoemd), is de specificatie voor functioneel veilige ontwerpen. Het documenteert de ontwerpflow die nodig is om een SIL-gecertificeerd onderdeel te ontwikkelen. Voor elke stap moet documentatie worden gegenereerd, van concept en definitie tot en met ontwerp, lay-out, fabricage, assemblage en testen.

Dit proces staat bekend als Route 1S en is ingewikkeld. Er is echter een alternatief voor Route 1S, namelijk de Route 2S-flow. Deze route is ‘proven in use’ en is van toepassing wanneer grote volumes van het product zijn ontworpen in eindproducten en systemen en worden gebruikt in het veld met duizenden uren van geaccumuleerd gebruik.

Onder Route 2S-flow kan een product nog steeds gecertificeerd worden door aan de certificeringsinstantie bewijs te leveren van:

- Volumes gebruikt in het veld

- Analyse van eventuele retourzendingen uit het veld en details dat de retourzendingen niet te wijten waren aan defecten in het onderdeel zelf

- Veiligheidsinformatieblad met details over de diagnoses en de dekking die ze bieden

- Pin- en chip-FMEDA

RTD-interfaces samenvoegen met SIL Route 2S-flow

Het certificeren van een systeem is een langdurig proces, omdat alle onderdelen in het systeem moeten worden beoordeeld op mogelijke storingsmechanismen en er verschillende methoden zijn om storingen vast te stellen. Het gebruik van onderdelen die al gecertificeerd zijn, vermindert het werk dat nodig is en verkort het certificeringsproces.

Een sterk geïntegreerde, goed ontwikkelde RTD-interfacecomponent is de sleutel tot het vergemakkelijken van Route 2S-certificering, omdat het een compleet oplossingspakket definieert en dus volledig kan worden gekarakteriseerd met gegevens over praktijkgebruik en storingen. Dit in tegenstelling tot het gebruik van meerdere kleinere bouwsteen-IC's, waarbij de verschillende interfaces en interacties moeten worden geanalyseerd voor de specifieke interconnectieconfiguratie die wordt gebruikt.

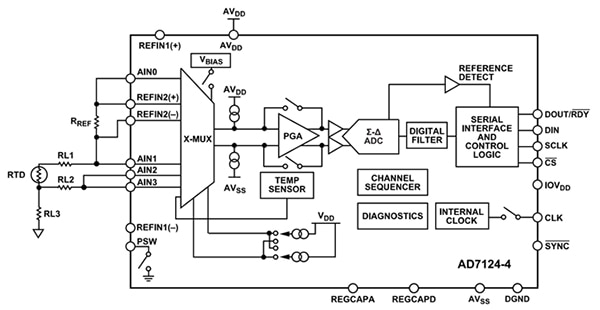

Een voorbeeld hiervan is de vierkanaals AD7124-4 (afbeelding 4) en de vergelijkbare achtkanaals AD7124-8 (hierna gezamenlijk aangeduid als de ‘AD7124’ bij het bespreken van de vele eigenschappen die ze gemeen hebben). Deze componenten passen goed bij de Route 2S-flow vanwege hun ingebouwde zelftest- en diagnosefuncties en hun ‘track record’ in het veld.

Afbeelding 4: De vierkanaals AD7124-4 is een functioneel complete RTD-sensor-naar-processorsignaalketen. (Bron afbeelding: Analog Devices)

Afbeelding 4: De vierkanaals AD7124-4 is een functioneel complete RTD-sensor-naar-processorsignaalketen. (Bron afbeelding: Analog Devices)

Deze IC's zijn complete oplossingen voor meerkanaals RTD-metingen en bevatten alle benodigde bouwstenen, van een sensor tot een gedigitaliseerde uitgang en voor communicatie met een bijbehorende microcontroller. Ze omvatten de meerkanaalsmultiplexer, PGA, 24-bit sigma-delta ADC, stroombronnen voor de RTD's, spanningsreferenties voor interne werking, systeemklok, analoge en digitale filtering en driedraads of vierdraads seriële interfaces voor SPI, QSPI, MICROWIRE en DSP-compatibele interconnecties.

De aanwezigheid van deze functies vormt echter niet automatisch een basis voor SIL Route 2S-kwalificatie. Voor een functioneel veilig ontwerp is een reeks ingebouwde diagnoses nodig voor de vele functies waaruit het RTD-systeem bestaat. De meervoudige ingebouwde diagnostiek in de AD7124 minimaliseert zowel de ontwerpcomplexiteit als de ontwerptijd, en maakt het dupliceren van de signaalketen voor diagnostische dekking overbodig.

Deze diagnostiek omvat, maar is niet beperkt tot, het bewaken van de voeding, referentiespanning en analoge ingang, het detecteren van een open draad naar de RTD's, het controleren van de conversie- en kalibratieprestaties, het controleren van de functionaliteit van de signaalketen, het bewaken van de lees-/schrijffuncties en het bewaken van de registerinhoud.

Hoe vertalen deze verklaringen op ‘hoog niveau’ zich naar de noodzakelijke diagnostiek op de chip? Het antwoord hierop heeft vele facetten, waaronder:

SPI-diagnose: voor elk schrijven naar de AD7124 genereert de processor een cyclische redundantiecontrole (CRC) die wordt toegevoegd aan de informatie die naar de ADC wordt gestuurd. De ADC genereert vervolgens zijn eigen CRC-waarde uit de ontvangen informatie en vergelijkt deze met de CRC-waarde die is ontvangen van de processor. Als beide waarden overeenkomen, is de informatie intact en wordt deze weggeschreven naar het relevante register op de chip.

Als de waarden niet overeenkomen, betekent dit dat de transmissie enigszins beschadigd is en dat het IC een foutvlag instelt die aangeeft dat de gegevens zijn beschadigd. De AD7124 beschermt zichzelf ook door de beschadigde informatie niet naar een register te schrijven.

Een vergelijkbare CRC-procedure wordt gebruikt wanneer informatie van de AD7124 naar de systeemprocessor wordt gelezen. En tot slot telt de interface ook klokpulsen om er zeker van te zijn dat er bij elk gegevensframe voor lezen of schrijven slechts acht van zulke pulsen zijn, zodat er geen klokstoring is opgetreden.

Geheugencontroles: een CRC wordt ook gebruikt om de registerinhoud te valideren bij het inschakelen of wanneer registers op de chip worden gewijzigd (zoals bij het wijzigen van de versterking). Het CRC-proces wordt ook periodiek uitgevoerd om er zeker van te zijn dat er geen geheugenbit door ruis of andere oorzaken is ‘omgedraaid’. Als er een wijziging is en de processor vervolgens de melding krijgt dat de registerinstellingen zijn beschadigd, kan de processor de ADC resetten en de registers opnieuw laden.

Signaalketencontroles: alle kritieke statische spanningen kunnen worden gecontroleerd via de ADC, inclusief voedingssporen, LDO (low-dropout) regelaaruitgangen en referentiespanningen. De aan- of afwezigheid van de externe condensator over de LDO kan ook worden gecontroleerd. Daarnaast kan een bekende spanning op de ADC-ingang worden gezet om de ADC en de instellingen van de versterkingsfunctie te controleren. Verder kunnen bekende stromen door de analoge ingangen worden gestuurd om te controleren op een open of kortgesloten RTD.

Conversie en kalibratie: de resultaten van de ADC-conversie worden continu gecontroleerd om te zien of ze naar alleen nullen of volle schaal gaan, wat op een probleem duidt. De bitstroom van de modulator in de kern van de ADC wordt gecontroleerd om er zeker van te zijn dat deze niet verzadigd is. Als er echter verzadiging optreedt (wat betekent dat er 20 opeenvolgende enen of nullen uit de modulator zijn gekomen), wordt er een foutvlag geplaatst.

Hoofdklokfrequentie: de frequentie van deze klok regelt niet alleen de conversiesnelheden, maar bepaalt ook de notchfrequenties van de 50/60 Hertz (Hz) digitale filters. Met een intern register in de AD7124 kan de begeleidende processor de tijd opnemen en zo de nauwkeurigheid van de masterklok controleren.

Extra functies: de AD7124 bevat een temperatuursensor, die ook kan worden gebruikt om de temperatuur van de chip te bewaken. Beide versies hebben een ESD-classificatie (electrostatic discharge) van 4 kilovolt (kV) voor robuuste prestaties, en beide zijn ondergebracht in een 5 × 5 millimeter (mm) LFCSP-behuizing dat geschikt is voor intrinsiek veilige ontwerpen.

Vanwege de interne complexiteit, verfijning en geavanceerde zelftestfuncties van de AD7124-4 en AD7124-8 is het handig om een manier te hebben om de IC's uit te proberen en te evalueren.

Daarom biedt Analog Devices een paar verbonden boards: het EVAL-AD7124-4SDZ evaluatieboard voor de AD7124-4 (afbeelding 5) en het bijbehorende EVAL-SDP-CB1Z SDP (System Demonstration Platform)/Interface Board (afbeelding 6). De eerste is specifiek voor de AD7124-4 en werkt samen met de tweede, die communicatie met de pc en evaluatiesoftware van de gebruiker verzorgt via een USB-verbinding.

Afbeelding 5: De EVAL-AD7124-4SDZ is een evaluatieboard voor de AD7124-4. (Bron afbeelding: Analog Devices)

Afbeelding 5: De EVAL-AD7124-4SDZ is een evaluatieboard voor de AD7124-4. (Bron afbeelding: Analog Devices)

Afbeelding 6: De EVAL-SDP-CB1Z/Interface Board is een aanvulling op de EVAL-AD7124-4SDZ-evaluatieboard en biedt een USB-verbinding met een host-pc. (Bron afbeelding: Analog Devices)

Afbeelding 6: De EVAL-SDP-CB1Z/Interface Board is een aanvulling op de EVAL-AD7124-4SDZ-evaluatieboard en biedt een USB-verbinding met een host-pc. (Bron afbeelding: Analog Devices)

De evaluatieopstelling wordt ondersteund door de AD7124-4 EVAL+ software, die de registerfunctionaliteit van de AD7124-4 volledig configureert en het IC stuurt. Deze opstelling biedt ook tijddomeinanalyse in de vorm van golfvormgrafieken, histogrammen en bijbehorende ruisanalyse voor de evaluatie van ADC-prestaties.

Overgang naar functioneel veilig ontwerp

Het is belangrijk om te weten dat de AD7124-4 en AD7124-8 geen SIL-classificatie hebben, wat betekent dat ze niet zijn ontworpen en ontwikkeld volgens de ontwikkelingsrichtlijnen van de IEC 61508-norm. Door echter de eindtoepassing te begrijpen en door het juiste gebruik van de verschillende diagnoses, kunnen ze worden beoordeeld voor gebruik in een SIL-geschikt ontwerp.

Voor het pad naar Route 1S-certificering moet rekening worden gehouden met diverse aandachtspunten voor het analyseren en aanpakken van storingen, die systemisch of willekeurig kunnen zijn. Systemische storingen zijn te wijten aan ontwerp- of fabricagefouten, zoals een noisy interrupt door een gebrek aan filtering op de externe interruptpin of onvoldoende headroom voor een signaal. Willekeurige storingen zijn daarentegen het gevolg van fysieke oorzaken zoals corrosie, thermische spanning of slijtage.

Een belangrijk probleem is de gevaarlijke onopgemerkte storing, die door meerdere technieken wordt aangepakt. Om willekeurige storingen te minimaliseren, gebruiken ontwerpers één of meerdere van deze tactieken:

- Betrouwbaardere, minder belaste componenten.

- Diagnostiek die vertrouwt op ingebouwde detectiemechanismen die zijn geïmplementeerd via hardware of software.

- Fouttolerantie via redundante circuits. Door een redundant pad toe te voegen, kan een enkele storing getolereerd worden. Dit wordt een Hardware Fault Tolerance 1 (HFT 1) systeem genoemd, wat betekent dat één storing niet kan leiden tot het uitvallen van het systeem.

Een hulpmiddel om de SIL-dekking te begrijpen is een matrix die de veilige uitvalfractie of ‘safe failure fraction’ (SFF) (de hoeveelheid diagnostische dekking) en de hardware fouttolerantie (de redundantie) in kaart brengt (afbeelding 7).

|

|||||||||||||||||||||||

Afbeelding 7: Deze matrix toont de veilige uitvalfractie (SFF) t.o.v. hardwarefouttolerantie (HFT) en geeft inzicht in SIL-dekking. (Bron afbeelding: Analog Devices)

De rijen tonen de hoeveelheid diagnostische dekking, terwijl de kolommen de hardwarefouttolerantie (HFT) weergeven. Een HFT van 0 betekent dat bij één fout in het systeem de veiligheidsfunctie verloren gaat. Een hoger diagnoseniveau verlaagt de benodigde hoeveelheid systeemredundantie of verbetert het SIL-niveau van de oplossing met hetzelfde redundantieniveau (lager in de matrix).

Merk op dat de FMEDA van een typische temperatuurtoepassing waarbij deze onderdelen worden gebruikt een veilige uitvalfractie (SFF) laat zien van meer dan 90% volgens IEC 61508. Normaal gesproken zouden er twee traditionele ADC's nodig zijn om dit dekkingsniveau via redundantie te bieden, maar de AD4172 heeft slechts één ADC nodig, waardoor er aanzienlijk bespaard kan worden op de materiaallijst (BOM) en het printplaatoppervlak.

Documentatie voor ontwerpen met SIL-classificatie

Er is uitgebreide documentatie nodig om de Route 1S-certificering te behalen. De benodigde brondocumenten zijn onder andere:

- Veiligheidsinformatieblad (de veiligheidshandleiding voor een onderdeel met SIL-classificatie)

- Pin-FMEDA en chip-FMEDA, met storingsmodi, effecten en analyse voor beide

- Bijlage F checklist (gedefinieerd door IEC 61508)

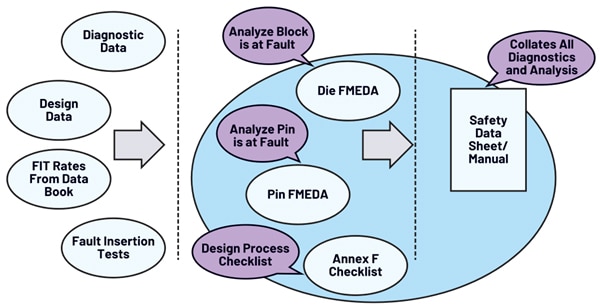

Deze documentatie is afkomstig uit verschillende bronnen (afbeelding 8):

- Diagnostische gegevens van het gegevensblad bevatten alle diagnostische functies die beschikbaar zijn in het onderdeel.

- Ontwerpgegevens verwijzen naar interne gegevens. Bijvoorbeeld het chipoppervlak en de impact van elk interne blok van het onderdeel.

- FIT, met cijfers voor verschillende onderdelen, zijn beschikbaar in het gegevensboek.

- Fault insertion tests worden uitgevoerd voor blokken die niet kunnen worden geanalyseerd met behulp van ontwerp- en diagnostische gegevens. Deze tests worden gepland op basis van de toepassingseisen en de resultaten van de tests worden gebruikt om de FMEDA- en FMEA-documenten te versterken.

Afbeelding 8: De verschillende documentatiebronnen worden samengevoegd tot het complete informatiepakket dat nodig is voor de SIL-certificering. (Bron afbeelding: Analog Devices)

Afbeelding 8: De verschillende documentatiebronnen worden samengevoegd tot het complete informatiepakket dat nodig is voor de SIL-certificering. (Bron afbeelding: Analog Devices)

Laten we de details eens nader bekijken:

- De veiligheidshandleiding of het veiligheidsinformatieblad gebruikt alle verzamelde informatie om de noodzakelijke vereisten te bieden om de integratie van de AD7124-4 of AD7124-8 mogelijk te maken. Het verzamelt alle diagnoses en analyses uit verschillende documenten en gegevenssets.

- De FMEDA voor de AD7124-4 en AD7124-8 analyseert de hoofdblokken in het toepassingsschema, identificeert storingsmodi en effecten en controleert de diagnose en analyses voor een bepaalde veiligheidsfunctie. De analyse van de klokmodule toont bijvoorbeeld de storingsmodi, het effect van elke modus op de uitvoer, de hoeveelheid diagnostische dekking en een analyse van de impact (afbeelding 9).

|

Afbeelding 9: Deze tabel definieert de storingsmodus, effecten, diagnostiek en analyse van het masterklokblok. (Bron afbeelding: Analog Devices)

Deze chip-FMEDA resulteert in een kwantitatieve presentatie van uitvalspercentages voor veilige fouten, gevaarlijke gedetecteerde fouten en gevaarlijke niet-gedetecteerde fouten. Al deze gegevens worden gebruikt om de SFF te berekenen.

De pin-FDEMA bekijkt storingen vanuit een ander perspectief. Het analyseert verschillende soorten storingen op de pinnen van de AD7124-4 en AD7124-8 en hun gevolgen voor de RTD-toepassing. Dit gebeurt voor elke afzonderlijke pin en het beschrijft het resultaat voor het geval dat de pin opengaat, kortsluiting maakt met de voeding/aarde of kortsluiting maakt met aangrenzende pins.

De bijlage F checklist is een controlelijst met ontwerpmaatregelen om systematische storingen te voorkomen. Het bestaat uit:

- Productoverzicht

- Toepassingsinformatie

- Veiligheidsconcept

- Voorspellingen levensduur

- FIT

- FMEDA-berekeningen: SFF en DC

- Hardware veiligheidsmechanismen

- Diagnosebeschrijving

- EMC-robuustheid

- Werking in redundante configuraties

- Bijlagen en documentenlijst

Samengevat is de functionele veiligheidscertificering voor een nieuw geïntroduceerd onderdeel via Route 1S een lang, complex, tijdrovend, intensief en veelomvattend proces. Gelukkig is Route 2S een alternatieve aanpak die voor sommige onderdelen levensvatbaar is, zoals hierboven vermeld.

Route 2S: een alternatief pad

Het pad staat bekend als Route 2S en is van toepassing op een vrijgegeven onderdeel met praktijkervaring en -gegevens, en wordt aangeduid als ‘proven in use’ (bewezen in gebruik). Het is gebaseerd op een analyse van de retourzendingen van klanten en het aantal verzonden apparaten. Het kan niet worden gebruikt voor nieuwe onderdelen die weinig of geen ‘blootstellingsverleden’ hebben bij daadwerkelijk gebruik.

Route 2S maakt SIL-certificering mogelijk alsof het onderdeel volledig is geanalyseerd volgens de IEC 61508-norm. Het is beschikbaar voor module- en systeemontwerpers als ze het betreffende IC in het verleden met succes hebben gebruikt en het storingspercentage uit de praktijk kennen. De ingebouwde test- en verificatiefuncties, samen met de prestatiegegevens, maken de AD7214-4 en AD7214-8 goede kandidaten voor Route 2S.

Route 2S vereist gedetailleerde en statistisch significante gegevens over retourzendingen en storingen in het veld. Voor IC-leveranciers is het veel moeilijker om aan deze vereiste te voldoen dan voor leveranciers van printplaten of modules. De reden hiervoor is dat leveranciers over het algemeen onvoldoende kennis hebben van de uiteindelijke toepassing, of welk percentage van de defecte eenheden uit het veld naar hen wordt teruggestuurd voor analyse.

Conclusie

Het Route 1S-pad voor functioneel veilige certificering van nieuwe producten is grondig, uitgebreid en gedetailleerd. Het is ook technisch uitdagend en zeker tijdrovend. Het Route 2S-proces daarentegen maakt het mogelijk om vrijgegeven producten te certificeren op basis van praktijkervaringen, storingen en analysegegevens. Dit is een handige route die wordt ondersteund door de AD7214-4 en AD7214-8 RTD-interface-IC's, omdat ze de vereiste geschiedenis hebben. Net zo belangrijk is dat deze IC's veel diagnostische en zelftestfuncties en eigenschappen bevatten, waardoor ze geschikte kandidaten zijn voor een dergelijke certificering.

Gerelateerde inhoud

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.