Hoe FPGA SoC's te gebruiken voor veilige en verbonden harde real-time systemen

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2023-02-16

FPGA's (Field Programmable Gate Arrays), voor Linux geschikte RISC-V-microcontroller unit (MCU) subsystemen, geavanceerde geheugenarchitecturen en krachtige communicatie-interfaces zijn belangrijke hulpmiddelen voor ontwerpers. Dit geldt met name voor ontwerpers van veilige verbonden systemen, veiligheidskritische systemen en een breed scala van harde real-time deterministische systemen zoals kunstmatige intelligentie (AI) en machinaal leren (ML).

De integratie van die verschillende elementen in een veilig, verbonden en deterministisch systeem kan echter een uitdagende en tijdrovende bezigheid zijn, evenals het leggen van de hogesnelheidsinterconnecties voor de verschillende systeemelementen. Ontwerpers moeten een geheugenbeheereenheid, geheugenbeschermingseenheid, veilige opstartmogelijkheid en gigabit-klasse zendontvangers voor hogesnelheidsconnectiviteit opnemen. Het ontwerp zal een actief en statisch vermogensbeheer en regeling van inschakelstromen nodig hebben. Sommige ontwerpen moeten werken in het uitgebreide commerciële temperatuurbereik van 0 °C tot +100 °C junctietemperatuur (TJ), terwijl systemen in industriële omgevingen moeten werken met TJ van -40 °C tot +100 °C.

Om deze en andere uitdagingen aan te gaan, kunnen ontwerpers zich wenden tot FPGA system-on-chip (SoC) apparaten die een laag stroomverbruik, thermische efficiëntie en defensieve beveiliging combineren voor slimme, verbonden en deterministische systemen.

Dit artikel bespreekt de architectuur van een dergelijke FPGA SoC en hoe deze het efficiënte ontwerp van verbonden en deterministische systemen ondersteunt. Vervolgens wordt kort de EEMBC CoreMark-Pro processing power versus power consumption benchmark gepresenteerd, samen met een overzicht van de benchmarkprestaties van een representatieve FPGA SoC. Er wordt gekeken hoe beveiliging in deze FPGA SoC's is ingebouwd en er worden voorbeelden gegeven van FPGA SoC's van Microchip Technology, samen met een ontwikkelingsplatform om het ontwerpproces te versnellen. Er wordt afgesloten met een korte opsomming van uitbreidingsborden van MikroElektronika waarmee een reeks communicatie-interfaces kan worden geïmplementeerd, alsmede een GNSS-locatiemogelijkheid (Global Navigation Satellite System).

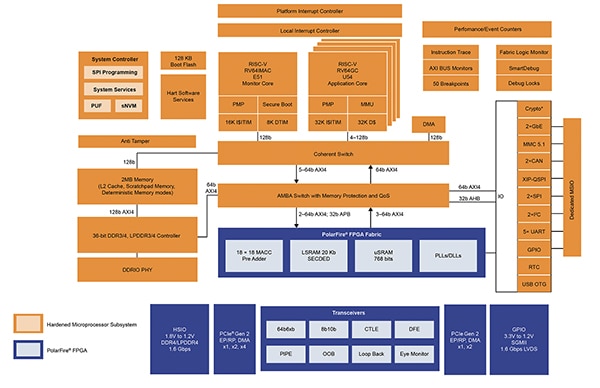

SoC's gebouwd met een FPGA-weefsel

De "chip" voor deze SoC is een FPGA-weefsel dat de systeemelementen bevat, van de FPGA tot het RISC-V MCU-subsysteem dat is opgebouwd met geharde FPGA-logica. Het MCU-subsysteem omvat een quad-core RISC-V MCU-cluster, een RISC-V-monitorkern, een systeemcontroller en een deterministisch Level 2 (L2) geheugensubsysteem. De FPGA in deze SoC's bevat tot 460 K logische elementen, tot 12,7 gigabit per seconde (Gbps) zendontvangers, en andere input/output (I/O) blokken, waaronder general purpose I/O (GPIO) en Peripheral Component Interconnect Express (PCIe) 2. De algemene architectuur is ontworpen met het oog op betrouwbaarheid. Het omvat foutcorrectie en dubbele foutdetectie (SECDED) op alle geheugens, differentiële vermogensanalyse (DPA), fysieke geheugenbescherming en 128 kilobits (Kbits) flash-opstartgeheugen (Afbeelding 1).

Afbeelding 1: Alle elementen in deze FPGA SoC, inclusief de RISC-V-subsystemen, zijn geïmplementeerd op het FPGA-weefsel. (Bron afbeelding: Microchip Technology)

Afbeelding 1: Alle elementen in deze FPGA SoC, inclusief de RISC-V-subsystemen, zijn geïmplementeerd op het FPGA-weefsel. (Bron afbeelding: Microchip Technology)

Microchip biedt zijn Mi-V (uitgesproken als "mijn vijf") ecosysteem van hulpmiddelen van derden en ontwerpmiddelen ter ondersteuning van de implementatie van RISC-V-systemen. Het is gebouwd om de invoering van de RISC-V-instructiesetarchitectuur (ISA) voor geharde RISC-V-kernen en voor RISC-V zachte kernen te versnellen. Elementen van het Mi-V-ecosysteem omvatten toegang tot:

- Intellectuele eigendom (IP) licenties

- Hardware

- Besturingssystemen en middleware

- Debuggers, compilers en ontwerpdiensten

De geharde RISC-V MCU's in de FPGA SoC bevatten diverse debugmogelijkheden, zoals passieve run-time configureerbare geavanceerde uitbreidbare interface (AXI) en instructietracering. Met AXI kunnen ontwerpers gegevens controleren die worden geschreven naar of gelezen uit verschillende geheugens en weten wanneer ze worden geschreven of gelezen.

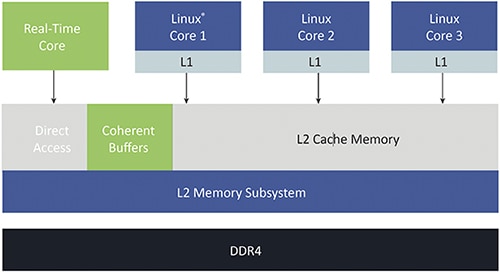

Het RISC-V MCU-subsysteem gebruikt een uit vijf fasen bestaande, in-order pijplijn. Hij is niet kwetsbaar voor Spectre- of Meltdown-exploits die buiten-orde-architecturen kunnen treffen. Alle vijf MCU's zijn coherent met het geheugensubsysteem en ondersteunen een mix van deterministische asymmetrische multi-processing (AMP) modus real-time systemen en Linux. De mogelijkheden van het RISC-V-subsysteem omvatten (Afbeelding 2):

- Linux en harde real-time operaties uitvoeren

- L1 en L2 configureren als deterministisch geheugen

- DDR4-geheugensubsysteem

- Vertakkingsvoorspellers uitschakelen/inschakelen

- In-order pijplijnoperatie

Afbeelding 2: Het RISC-V-subsysteem omvat verschillende processor- en geheugenelementen. (Bron afbeelding: Microchip Technology)

Afbeelding 2: Het RISC-V-subsysteem omvat verschillende processor- en geheugenelementen. (Bron afbeelding: Microchip Technology)

Meer verwerking met minder energie

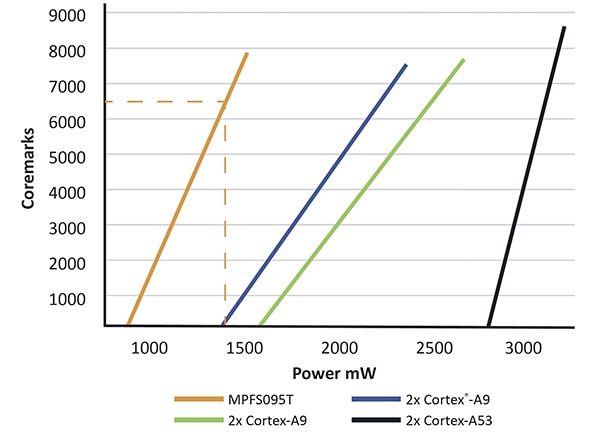

Deze FPGA SoC's bieden niet alleen voordelen op het gebied van systeemwerking, waaronder ondersteuning voor harde, real-time verwerking, maar zijn ook zeer energiezuinig. De EEMBC CoreMark-PRO-benchmark is een industriestandaard voor het vergelijken van de efficiëntie en prestaties van MCU's in ingebedde systemen. Het is speciaal ontworpen om hardwareprestaties te benchmarken en om de Dhrystone benchmark te vervangen.

De CoreMark-PRO-workloads omvatten een verscheidenheid aan prestatiekenmerken, parallellisme op instructieniveau en geheugengebruik op basis van vier floating-point workloads en vijf gewone integer-workloads. De floating-point-workloads omvatten een lineaire algebra routine afgeleid van LINPACK, een snelle Fourier-transformatie, een neuraal net-algoritme voor patroonevaluatie, en een verbeterde versie van de Livermore loops benchmark. JPEG-compressie, een XML-parser, ZIP-compressie en een 256-bits veilig hash-algoritme (SHA-256) vormen de basis van de integer workloads.

De MPFSO95T-modellen van deze SoC FPGA's, zoals de MPFS095TL-FCSG536E, kunnen tot 6.500 Coremarks leveren bij 1,3 watt (Afbeelding 3).

Afbeelding 3: De MPFS095T FPGA SoC (oranje lijn) levert 6500 Coremarks bij 1,3 watt. (Bron afbeelding: Microchip Technology)

Afbeelding 3: De MPFS095T FPGA SoC (oranje lijn) levert 6500 Coremarks bij 1,3 watt. (Bron afbeelding: Microchip Technology)

Veiligheidsoverwegingen

De veiligheidskritische en harde real-time toepassingen voor deze FPGA SoC's vereisen sterke beveiliging naast hoge energie-efficiëntie en krachtige verwerkingscapaciteiten. De basisbeveiligingsfuncties van deze FPGA SoC's omvatten differentiële vermogensanalyse (DPA) bestendige bitstroomprogrammering, een true random number generator (TRNG) en een fysiek niet-klikbare functie (PUF). Ze omvatten ook standaard en door de gebruiker gedefinieerde beveiligde opstart, fysieke geheugenbescherming die geheugentoegangsbeperkingen biedt in verband met de machtigingsstatus van de machine, inclusief machine-, supervisor- of gebruikersmodi, en immuniteit tegen Meltdown- en Spectre-aanvallen.

Beveiliging begint met een veilig beheer van de toeleveringsketen, waaronder het gebruik van hardwarebeveiligingsmodules (HSM's) tijdens het testen en verpakken van wafers. Het gebruik van een 768-bytes digitaal ondertekend x.509 FPGA-certificaat in elke FPGA SoC draagt bij tot de zekerheid van de toeleveringsketen.

Deze FPGA SoC's bevatten tal van on-chip sabotagedetectoren om een veilige en betrouwbare werking te garanderen. Als sabotage wordt geconstateerd, wordt een sabotagevlag afgegeven waarmee het systeem indien nodig kan reageren. Enkele van de beschikbare sabotagedetectors zijn:

- Spanningscontroles

- Temperatuursensors

- Detectors voor klokfouten en klokfrequentie

- JTAG actieve detector

- Netwerk actieve detector

De beveiliging is verder verzekerd met 256-bit geavanceerde encryptiestandaard (AES-256) symmetrische blokcijfercorrelatie power attack (CPA) tegenmaatregelen, geïntegreerde cryptografische digest-mogelijkheden om gegevensintegriteit te verzekeren, geïntegreerde PUF voor sleutelopslag en zeroization-mogelijkheden voor de FPGA-structuur en alle on-chipgeheugens.

FPGA SoC-voorbeelden

Microchip Technology combineert deze mogelijkheden en technologieën in zijn PolarFire FPGA SoC's met meerdere snelheidsgraden, temperatuurwaarden en verschillende verpakkingsgroottes om te voorzien in de behoeften van ontwerpers voor een breed scala aan oplossingen met 25 tot 460 K logica-elementen. Er zijn vier temperatuurklassen beschikbaar (allemaal geschikt voor TJ), 0 °C tot +100 °C uitgebreid commercieel bereik, -40 °C tot +100 °C industrieel bereik, -40 °C tot +12 5°C voor auto's en -55 °C tot +125 °C militair bereik.

Ontwerpers kunnen kiezen uit toestellen met standaardsnelheid of toestellen met -1 snelheid die 15% sneller zijn. Deze FPGA SoC's kunnen werken op 1,0 volt voor het laagste vermogen, of op 1,05 volt voor hogere prestaties. Ze zijn verkrijgbaar in verschillende verpakkingsformaten, waaronder 11 x 11 mm, 16 x 16 mm en 19 x 19 mm.

Voor toepassingen die een langere bedrijfstemperatuur, standaardsnelheid en 254 K logica-elementen in een 19 x 19 mm verpakking nodig hebben, kunnen ontwerpers de MPFS250T-FCVG484EES gebruiken. Voor eenvoudiger oplossingen die 23 K logica-elementen nodig hebben, kunnen ontwerpers zich wenden tot de MPFS025T-FCVG484E, eveneens met uitgebreide commerciële temperatuurwerking en standaard snelheidsgraad in een 19 x 19 mm pakket. De MPFS250T-1FCSG536T2 met 254 K logische elementen is ontworpen voor krachtige autosystemen en heeft een bedrijfstemperatuurbereik van -40 tot 125 °C en een snelheidsgraad van -1 voor een 15% snellere klok, in een compacte 16 x 16 mm verpakking met 536 bolletjes op een pitch van 0,5 mm (Afbeelding 4).

Afbeelding 4: De MPFS250T-1FCSG536T2 voor auto's wordt geleverd in een 16 x 16 mm verpakking met een ball count van 536 en een pitch van 0,5 mm. (Bron afbeelding: Microchip Technology)

Afbeelding 4: De MPFS250T-1FCSG536T2 voor auto's wordt geleverd in een 16 x 16 mm verpakking met een ball count van 536 en een pitch van 0,5 mm. (Bron afbeelding: Microchip Technology)

FPGA SoC-ontwikkelplatform

Om het ontwerp van systemen met de PolarFire FPGA SoC te versnellen, biedt Microchip de MPFS-ICICLE-KIT-ES PolarFire SoC Icicle-kit die het mogelijk maakt om het vijfkernige Linux-capabele RISC-V microprocessorsubsysteem te verkennen met low-power, real-time uitvoering. Het pakket bevat een gratis Libero Silver licentie die nodig is om ontwerpen te evalueren. Het ondersteunt programmeer- en debugfuncties in één enkele taal.

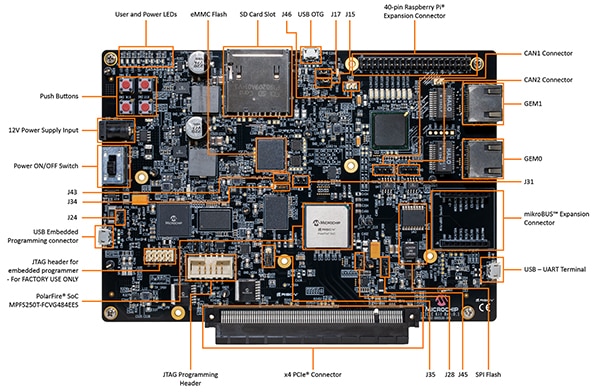

Deze FPGA SoC's worden ondersteund met de VectorBlox accelerator software development kit (SDK) die laag vermogen, AI/ML-toepassingen met een kleine vormfactor mogelijk maakt. De nadruk ligt op het vereenvoudigen van het ontwerpproces tot het punt dat ontwerpers geen eerdere ervaring met FPGA-ontwerp hoeven te hebben. Met de VectorBlox-accelerator SDK kunnen ontwikkelaars energie-efficiënte neurale netwerken programmeren met behulp van C/C++. De Icicle kit heeft talrijke functies om een uitgebreide ontwikkelingsomgeving te bieden, inclusief een multi-rail power sensor systeem om de verschillende power domains te monitoren, PCIe root poort, en onboard geheugens - inclusief LPDDR4, QSPI, en eMMC Flash - om Linux en Raspberry Pi te draaien, en mikroBUS uitbreidingspoorten voor een groot aantal bedrade en draadloze connectiviteitsopties, plus functionele uitbreidingen zoals GNSS locatie mogelijkheid (Afbeelding 5).

Afbeelding 5: Deze uitgebreide FPGA SoC-ontwikkelomgeving bevat connectors voor uitbreidingsborden voor Raspberry Pi (rechtsboven) en mikroBUS (rechtsonder). (Bron afbeelding: Microchip Technology)

Afbeelding 5: Deze uitgebreide FPGA SoC-ontwikkelomgeving bevat connectors voor uitbreidingsborden voor Raspberry Pi (rechtsboven) en mikroBUS (rechtsonder). (Bron afbeelding: Microchip Technology)

Uitbreidingsborden

Enkele voorbeelden van mikroBUS-uitbreidingsborden zijn:

MIKROE-986, voor het toevoegen van CAN-busconnectiviteit met behulp van een seriële perifere interface (SPI).

MIKROE-1582, voor interfacing tussen de MCU en een RS-232-bus.

MIKROE-989, voor aansluiting op een RS422/485-communicatiebus.

MIKROE-3144, ondersteunt de LTE Cat M1- en NB1-technologieën waardoor een betrouwbare en eenvoudige verbinding met 3GPP IoT-apparaten mogelijk is.

MIKROE-2670, maakt GNSS-functionaliteit mogelijk met gelijktijdige ontvangst van GPS- en Galileo-constellaties plus BeiDou of GLONASS, wat resulteert in hoge positienauwkeurigheid in situaties met zwakke signalen of interferentie in stedelijke ravijnen.

Conclusie

Ontwerpers kunnen een beroep doen op FPGA SoC's bij de ontwikkeling van verbonden, veiligheidskritische en harde realtime deterministische systemen. FPGA SoC's bieden een breed scala aan systeemelementen, waaronder een FPGA-weefsel, een RISC-V MCU-subsysteem met krachtige geheugens, snelle communicatie-interfaces en talrijke beveiligingsfuncties. Om ontwerpers op weg te helpen, zijn ontwikkelingskaarten en -omgevingen beschikbaar die alle noodzakelijke elementen bevatten, waaronder uitbreidingskaarten waarmee een groot aantal communicatie- en locatiefuncties kan worden geïmplementeerd.

Aanbevolen lectuur

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.