Voldoen aan diverse functionele en veiligheidseisen met multicoreprocessors

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2020-10-01

De verwachting is dat auto-, industrie-, robotica, gebouwenbeheer en andere kritische embedded systeemtoepassingen een grotere verscheidenheid aan werklasten op zich zullen nemen, variërend van low-power real-time monitoring tot hoogwaardige multimediatoepassingen met multiscreen grafische displays voor mens-machine-interfaces (HMI's). Terwijl ze aan deze brede functionele eisen voldoen, moeten ze ook in staat zijn om strenge veiligheidsnormen te ondersteunen, de kosten en de voetafdruk te verlagen en de balans tussen vermogen en prestaties te optimaliseren.

Om aan deze vaak tegenstrijdige eisen te voldoen, zijn ontwikkelaars tot nu toe gedwongen om ofwel functionele mogelijkheden op te offeren, ofwel het ontwerp en de productie te compliceren met toegevoegde apparaten die nodig zijn om specifieke eisen voor onder andere graphics, beveiliging en veiligheid te ondersteunen. Wat de ontwikkelaars echt nodig hebben, is een enkele oplossing die in staat is om een breed scala aan producten te ondersteunen die aan deze eisen voldoen in een breed scala aan kritische embedded systeemtoepassingen.

In dit artikel wordt snel de evolutie van het kritisch ingebedde systeemontwerp beschreven. Het zal dan laten zien hoe multicore-applicatieprocessors, specifiek ontworpen door NXP Semiconductors om een snel uitbreidende lijst van eisen voor zowel brede functionaliteit als veiligheidscertificering te ondersteunen, kunnen worden gebruikt om de uitdagingen van ontwikkelaars aan te pakken.

De evolutie van ingebedde systeemontwerpoverwegingen

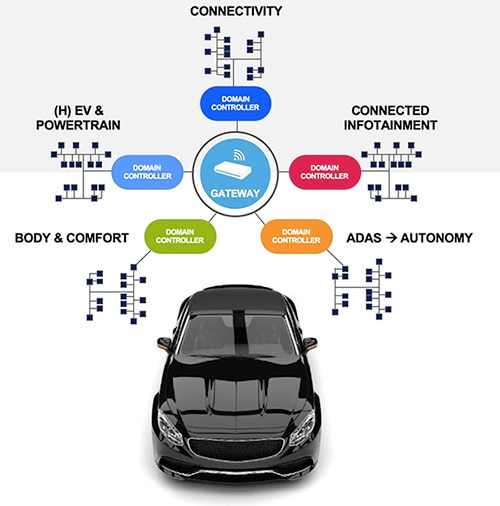

De traditionele rol van ingebedde apparaten bij de ondersteuning van een beperkte reeks systeemfuncties is grotendeels vervangen door de vraag naar apparaten die brede mogelijkheden bieden. In industriële toepassingen vraagt de behoefte aan verbeterde HMI-mogelijkheden in slimme tools en apparatuur om processors die in staat zijn om geoptimaliseerde graphics te leveren en tegelijkertijd te voldoen aan de meer traditionele industriële real-time vereisten. Evenzo drijft de trend in automobieltoepassingen naar hiërarchische architecturen die functionele domeinclusters en gateways omvatten, een behoefte aan processors die volledig aan deze vereisten kunnen voldoen (Afbeelding 1).

Afbeelding 1: De trend naar meer hiërarchische automotive systeemarchitecturen heeft geleid tot een behoefte aan meer geïntegreerde, schaalbare processoroplossingen. (Bron afbeelding: NXP Semiconductors)

Afbeelding 1: De trend naar meer hiërarchische automotive systeemarchitecturen heeft geleid tot een behoefte aan meer geïntegreerde, schaalbare processoroplossingen. (Bron afbeelding: NXP Semiconductors)

Binnen elk functioneel domein blijft de vraag naar meer geavanceerde mogelijkheden de drempel voor prestaties en geïntegreerde mogelijkheden verhogen. De opkomst van heads-up displays vraagt bijvoorbeeld om oplossingen die ervoor kunnen zorgen dat essentiële grafische informatie aan de chauffeurs blijft worden geleverd. Samen met deze volgende-generatie displays, voegt de groeiende behoefte aan een betere bewustwording van de bestuurder extra eisen toe aan de interfaces van de camera en de krachtige uitvoering van geavanceerde herkenningssoftware die in staat is om slaperigheid te detecteren.

Naarmate applicaties zich blijven ontwikkelen, wordt de behoefte aan sterk geïntegreerde, schaalbare oplossingen dringender om aan de steeds diverser wordende eisen te voldoen en tegelijkertijd de ontwerpvoetafdruk, de kosten en de complexiteit te minimaliseren. Met behulp van NXP's i.MX 8-familie van applicatieprocessors, kunnen ontwikkelaars gebruik maken van een compatibel platform van processors met het scala aan mogelijkheden en prestaties die nodig zijn om een breed scala aan applicatievereisten te ondersteunen. Binnen de i.MX 8-serie komt de NXP i.MX 8X-serie tegemoet aan opkomende behoeften aan veiligheidscertificerende processors die nodig zijn in het middensegment van de auto- en industriële toepassingen.

Multicore-architectuur beheert diverse werklasten

Een van de problemen die ontwikkelaars ondervinden bij de implementatie van apparaten voor automobiel- en industriële toepassingen is de grote omvang van de eisen. Waar ontwikkelaars konden verwachten dat ze te maken zouden krijgen met real-time of hoog niveau van applicatieverwerking, heeft de vraag naar intelligente subsystemen deze significant verschillende soorten van computing samengevoegd. Ontwikkelaars hebben steeds meer behoefte aan oplossingen die in staat zijn om zowel een betrouwbare real-time respons als een krachtige applicatie-uitvoering te leveren en tegelijkertijd de functionele veiligheidseisen te ondersteunen.

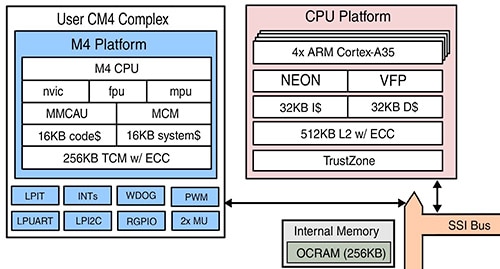

De NXP i.MX 8X-serie processors zijn ontworpen om real-time mogelijkheden, hoogwaardige verwerking en een laag stroomverbruik te leveren en maken optimaal gebruik van een geavanceerde multicore centrale verwerkingseenheid (CPU-architectuur) om diverse rekenkundige werklasten te beheren (Afbeelding 2).

Afbeelding 2: De NXP i.MX 8X-serie maakt gebruik van een multicore-architectuur bestaande uit een Arm Cortex-M4 (CM4) embedded processor en meerdere Arm Cortex-A35 applicatieprocessoren om gemengde software werklasten te ondersteunen. (Bron afbeelding: NXP Semiconductors)

Afbeelding 2: De NXP i.MX 8X-serie maakt gebruik van een multicore-architectuur bestaande uit een Arm Cortex-M4 (CM4) embedded processor en meerdere Arm Cortex-A35 applicatieprocessoren om gemengde software werklasten te ondersteunen. (Bron afbeelding: NXP Semiconductors)

Voor algemene real-time verwerkingstaken omvatten i.MX 8X apparaten een Arm Cortex-M4 (CM4) processor met floating point unit (FPU), memory protection unit (MPU), memory mapped cryptographic acceleration unit (MMCAU) en diverse besturingsmodules (MCM). Ter ondersteuning van externe randapparatuur zoals sensoren en actuatoren, combineert dit gebruikerscomplex CM4 een genestelde vectorinterruptregelaar (NVIC) met een uitgebreide set interfaces en modules, waaronder een laagvermogen periodieke interrupttimer (LPIT), pulsbreedtemodulatie (PWM), en andere functies die gewoonlijk vereist zijn in auto- en industriële toepassingen. Een paar cachegeheugens en strak gekoppeld geheugen (TCM) met foutcorrectiecode (ECC) helpt de toegang tot het externe geheugen, de snelheidsuitvoering en het omgaan met geheugenfouten tot een minimum te beperken.

Voor een snelle uitvoering van applicatiewerklasten bestaat het CPU-platform uit meerdere energiezuinige Arm Cortex-A35 applicatieprocessors (AP's)-twee AP's in 8DualXPlus-processors zoals de MIMX8UX6AVLFZAC, en vier AP's in 8QuadXPlus-processors zoals de MIMX8QX6AVLFZAC. Samen met speciale instructie (I$) en data (D$) cache, bevat het CPU-platform een gedeelde 512 kilobyte (Kbyte) niveau 2 (L2) cache met ECC.

De Arm Cortex-A35-kernen van de architectuur bieden zowel softwarecompatibiliteit als performance-schaalbaarheid en ondersteunen zowel 32-bits achterwaartse compatibiliteit als 64-bits performance. Om de uitvoering van rekenintensieve algoritmen zoals signaalverwerking en machinaal leren verder te versnellen, bieden de Arm Cortex-A35 processoren vector floating point (VFP) verwerking en Arm's Neon single instruction multiple data (SIMD) architectuur extensies. Om de uitvoering van software voor beeldverwerking, computervisie en machinaal leren te versnellen, biedt de Arm Compute Library functies die geoptimaliseerd zijn voor Arm processor en grafische verwerkingseenheid (GPU) architecturen, en de open source Ne10 C-bibliotheek biedt functies die geoptimaliseerd zijn voor de Arm-intensieve operaties.

Toegewijde engines ontlasten primaire CPU's

Naast het CM4-complex van de gebruiker en het multicore CPU-platform Arm Cortex-A35 biedt de architectuur extra speciale engines voor multimediatoepassingen. Samen met een digitale signaalprocessor (DSP) voor audio- en spraakcodec-processing, integreert de architectuur zowel een GPU als een videoverwerkingseenheid (VPU). De GPU van het apparaat ondersteunt standaard grafische bibliotheken en versnelt de werkzaamheden met behulp van vier afzonderlijke viercomponenten zwevende puntvectoren (vec4) met 16 uitvoeringseenheden en een krachtige, tweedimensionale bitblitmotor. De VPU verwerkt populaire videoformaten en versnelt de decodering tot 4Kp30 (progressief, 30 Hz) en de codering tot 1080p30. Op zijn beurt kan het speciale display-controllerblok van de chip grafische uitvoer naar maar liefst drie onafhankelijke displays sturen.

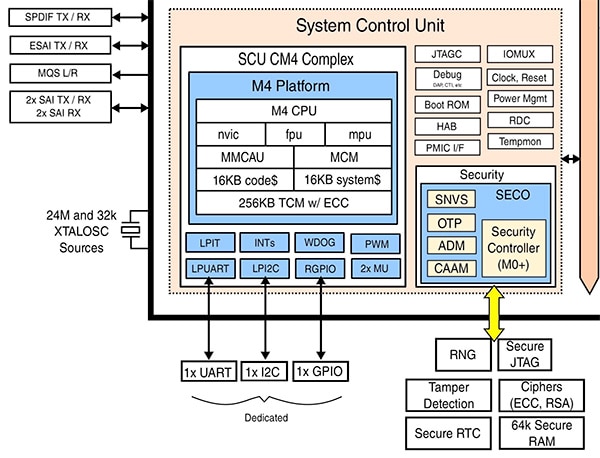

Om de prestaties verder te maximaliseren, integreert de i.MX 8X-architectuur ook extra processorkernen die zijn ontworpen om de primaire CPU-platforms te bevrijden van de extra verwerkingsbelasting die normaal gesproken optreedt bij het uitvoeren van systeembeheer- en beveiligingsdiensten. Voor systeembeheer integreert de systeembesturingseenheid (SCU) van de architectuur een CM4-complex dat overeenkomt met het CM4-complex van de gebruiker, maar volledig gewijd blijft aan SCU-bewerkingen en niet beschikbaar is voor gebruik door ontwikkelaars (Afbeelding 3).

Afbeelding 3: Geïntegreerd diep in NXP i.MX 8X-processors en niet beschikbaar voor ontwikkelaars, gebruikt de SCU een speciaal Arm Cortex-M4 (CM4) subsysteem om systeembeheertaken te ontladen van de hoofdprocessors van het apparaat. (Bron afbeelding: NXP Semiconductors)

Afbeelding 3: Geïntegreerd diep in NXP i.MX 8X-processors en niet beschikbaar voor ontwikkelaars, gebruikt de SCU een speciaal Arm Cortex-M4 (CM4) subsysteem om systeembeheertaken te ontladen van de hoofdprocessors van het apparaat. (Bron afbeelding: NXP Semiconductors)

Samen met het beheer van de voeding, de klok en andere interne functies, regelt de SCU de pin-multiplexing en de aandrijfkracht van het in-/uitgangskanaal (I/O) in normaal bedrijf. In feite kan de gebruiker CM4 complex en Arm Cortex-A35 AP's niet direct toegang krijgen tot deze verschillende low-level hardware mogelijkheden. In plaats daarvan dient de SCU om deze mogelijkheden te abstraheren, dus software die draait op de gebruiker CM4 of AP's hoeft alleen maar SCU-firmware applicatie programmeerinterface (API) functies aan te roepen om functies uit te voeren zoals het aanzetten van onnodige stroomdomeinen. Als dat stroomdomein bijvoorbeeld wordt gedeeld met een andere processor, erkent de SCU eenvoudigweg het verzoek om het domein uit te schakelen, maar houdt het domein aan totdat die andere processor ook een verzoek om het domein uit te schakelen afgeeft.

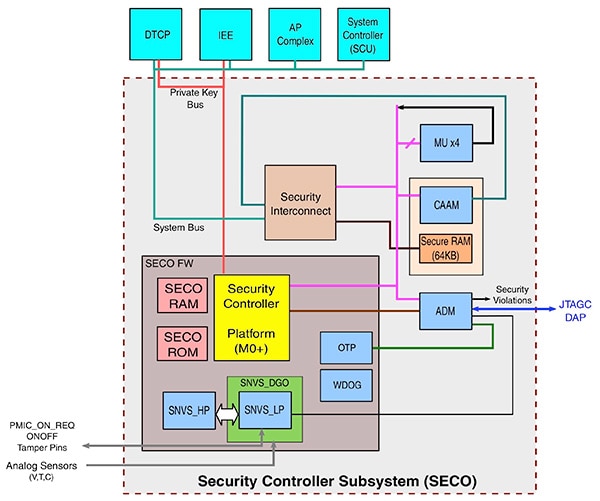

Om de uitgebreide beveiligingsondersteuning van de i.MX 8X te beheren, wordt een andere speciale processor gebruikt in het SECO-subsysteem (Security Controller) van het apparaat. Binnen het SECO-subsysteem voert een geïntegreerde low-power Arm Cortex-M0+ processor firmware uit die hardwarematige beveiligingsmogelijkheden ondersteunt, waaronder een privé-bustoegang voor veilige sleutels, een eenmalig programmeerbaar (OTP) geheugen voor veilige sleutelopslag en veilige niet-vluchtige opslag (SNVS) voor extra privégegevens of efemere sleutels (Afbeelding 4).

Afbeelding 4: Binnen het NXP i.MX 8X security controller (SECO) subsysteem beheert een speciale low-power Arm Cortex-M0+ processor beveiligingsoperaties, waarbij gebruik wordt gemaakt van een private key bus en meerdere hardwaremodules voor veilige opslag, cryptografieversnelling en geverifieerde debugtoegang. (Bron afbeelding: NXP Semiconductors)

Afbeelding 4: Binnen het NXP i.MX 8X security controller (SECO) subsysteem beheert een speciale low-power Arm Cortex-M0+ processor beveiligingsoperaties, waarbij gebruik wordt gemaakt van een private key bus en meerdere hardwaremodules voor veilige opslag, cryptografieversnelling en geverifieerde debugtoegang. (Bron afbeelding: NXP Semiconductors)

Naast deze kernbeveiligingsmechanismen coördineert het SECO-subsysteem beveiligingsoperaties voor sabotagedetectie en beveiligde debuggen via zijn Authenticated Debug Module (ADM). Voor een veilige uitvoering ondersteunt de geïntegreerde Cryptografische Versnellings- en Assurantiemodule (CAAM) een volledige reeks beveiligingsalgoritmen, waaronder symmetrische en asymmetrische cryptografie, hash-functies en een random number generator (RNG).

Bij normaal gebruik maken de apparaatverwerkende eenheden, waaronder de SCU, AP's en Digital Transport Content Protection (DTCP) versneller, gebruik van de SECO-veiligheidsinterconnectie om toegang te krijgen tot de CAAM-functionaliteit via de systeembus. Behalve toegang via de CAAM-functionaliteit (DMA) kan de speciale Cortex-M0+ processor van de SECO geen toegang krijgen tot de systeembus. In plaats daarvan maakt het gebruik van beveiligde interne verbindingen om toegang te krijgen tot randapparatuur, beveiligd random access geheugen (RAM) en alleen-lezen geheugen (ROM), en zijn speciale privé-sleutelbus.

Samen met het gebruik van de DTCP-versneller speelt deze privé-sleutelbus een centrale rol in de i.MX 8X-processorondersteuning voor on-the-fly versleuteling en ontcijfering. Hier gebruikt de veiligheidsprocessor zijn middelen om de privé-sleutels te leveren die nodig zijn voor de IEE-module (Inline Encryption/Decryption Engine) van het apparaat, terwijl deze veilig leest van of schrijft naar gecodeerde opslag, zonder tussenkomst van de verzoekende processor, DMA-controller of I/O-apparaat.

Voortbouwend op de TrustZone-technologie van Arm die in de Cortex-A35-processoren van het apparaat is geïntegreerd, werkt het SECO-subsysteem ook met de SCU tijdens het beveiligde opstartproces. In dit proces interpreteert de SCU de bootinstellingen, configureert hij de bootbronnen en laadt hij de bootafbeeldingen naar het interne of externe geheugen. Het SECO-subsysteem gebruikt op zijn beurt zijn cryptografiefuncties om ondertekende firmware-afbeeldingen te authenticeren nadat ze zijn geladen, maar voordat ze worden uitgevoerd.

Bescherming van kritieke displays en besturingsfunctionaliteit

Hoewel het vermogen om diverse werklasten efficiënt en veilig te verwerken belangrijk is, is het voor bedrijfskritische toepassingen zoals die in de automobielsector en de industrie net zo belangrijk om de belangrijkste capaciteiten veilig te stellen. De i.MXX 8X-familie van NXP combineert zijn verwerkingscapaciteiten met veiligheidscertificaten die nodig zijn om aan deze kritische eisen te voldoen.

De veiligheidsondersteuning van de processorfamilie is op een aantal niveaus ingebouwd, te beginnen met de fabricage in een volledig uitgeputte silicium op isolator (FD-SOI) procestechnologie die de betrouwbaarheid van het systeem verbetert. Omdat de veiligheid van het systeem afhankelijk is van een robuuste beveiligingsbasis, kan de combinatie van TrustZone-enabled AP's, het SECO-subsysteem, en veilige opstartmogelijkheden het soort vertrouwde omgeving bieden dat nodig is om bedreigingen voor de veiligheid en beveiliging tegen te gaan.

Tegelijkertijd helpt de mogelijkheid om onafhankelijk tijdskritische taken met de gebruiker CM4 complex af te handelen en kritische systeemtaken te ontladen aan de SCU en SECO subsystemen om ervoor te zorgen dat de bedrijfskritische applicatiemogelijkheden beschikbaar blijven ondanks de variërende verwerkingsbelasting. In feite breidt NXP dit concept uit tot ondersteuning van bedrijfskritische beeldschermen via de SafeAssure-technologie van het bedrijf, die een Automotive Safety Integrity Level B (ASIL B)-klaar hardwarematige weergavepad in i.MX 8X-apparaten integreert. Met SafeAssure worden gebruikers automatisch voorzien van een failover beeld als het apparaat een data-integriteit of GPU-fout detecteert. Op de achtergrond zorgt dit failoverbeeld ervoor dat kritieke informatie beschikbaar blijft, zelfs tijdens het uitvallen van het primaire beeldscherm.

De ondersteuning voor veiligheidstoepassingen strekt zich uit tot de toegang tot het geheugen in i.MX 8X-gebaseerde systemen. Onder hun ondersteunde geheugeninterfaces bieden i.MX 8X apparaten 8-bit ECC voor Dubbele Data Rate 3 laagspanning (DDR3L) geheugen. Samen met ECC in L2-cache (zie figuur 2) ondersteunt deze DDR3L ECC-capaciteit industriële veiligheidsintegriteit niveau 3 (SIL 3). De i.MX 8X-architectuur breidt de ECC-ondersteuning ook uit naar externe flashopslagapparaten. Hier zorgt een geïntegreerde Bose, Ray-Chaudhuri, Hocquenghem (BCH) encoder en decoder module voor 62-bit ECC die in staat is om 2 tot 20 single-bit fouten te corrigeren binnen een blok van gegevens die worden uitgelezen van deze opslagapparaten.

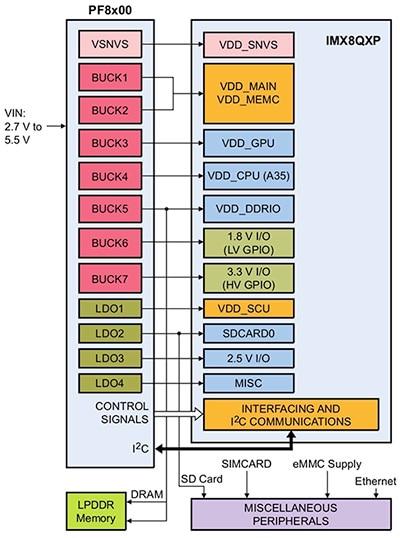

Het naar voren brengen van i.MX 8X-gebaseerde toepassingen

Zoals bij elke processor in deze klasse vereist de implementatie van een i.MX 8X-gebaseerd ontwerp zorgvuldige aandacht voor de strenge eisen die aan het vermogen worden gesteld, met inbegrip van kritieke inschakelsequenties. Voor het aanzetten van i.MX 8X-apparaten is het nodig om de stroom in volgorde of gelijktijdig naar vier verschillende voedingsgroepen te brengen, te beginnen met het SVNS-subsysteem en verder te gaan met de SCU, de I/O's en de geheugeninterfaces, en ten slotte de rest van het apparaat. Ontwikkelaars kunnen aan deze eis voldoen met behulp van NXP's PF8x00 power management integrated circuit (PMIC) apparaten, die een complete set spanningsrails en stuursignalen leveren die nodig zijn voor de ondersteuning van i.MX 8X-processoren, evenals extern geheugen en typische systeemrandapparatuur (Afbeelding 5).

Afbeelding 5: NXP PF8x00 PMIC's leveren een volledige set spanningsrails en stuursignalen die nodig zijn om i.MX 8X-processors van stroom te voorzien. (Bron afbeelding: NXP Semiconductors)

Afbeelding 5: NXP PF8x00 PMIC's leveren een volledige set spanningsrails en stuursignalen die nodig zijn om i.MX 8X-processors van stroom te voorzien. (Bron afbeelding: NXP Semiconductors)

Bij het implementeren van hun eigen i.MX 8X-gebaseerde ontwerpen kunnen ontwikkelaars gebruik maken van de NXP MC33PF8100CCES PMIC die is voorgeprogrammeerd voor gebruik met 8QuadXPlus-processors zoals de MIMX8QX6AVLFZAC. Andere PF8x00-varianten zoals de MC33PF8100A0ES en MC33PF8200A0ES ondersteunen i.MX 8X-processors, maar zijn niet voorgeprogrammeerd.

Voor veiligheidstoepassingen integreren apparaten van de PF8200-serie, zoals de MC33PF8200A0ES, functies die ontworpen zijn om ASIL B-systemen te ondersteunen. Samen met meerdere interne monitoren, waaronder een uitgangsspanningsmonitor met een speciale bandkloofreferentie, bevatten de PF8200 PMIC's een FSOB-pen (fail-safe output) die is ontworpen om het systeem in een veilige staat te houden tijdens het opstarten of tijdens een stroomonderbreking. Bovendien test een analoge ingebouwde zelftest (ABIST) alle spanningsmonitors terwijl een zelftestroutine de functionaliteit van andere apparaten controleert.

Hoewel PF8x00 PMIC's het hardwareontwerp van i.MX 8X-gebaseerde systemen kunnen vereenvoudigen, moeten sommige ontwikkelaars misschien onmiddellijk beginnen met het evalueren van i.MX 8X-apparaten en snel een prototype van i.MX 8X-gebaseerde toepassingen. NXP's MCIMX8QXP-CPU i.MX 8X Multisensory Enablement Kit (MEK) biedt een kant-en-klaar ontwikkelplatform dat een NXP i.MX 8QuadXPlus processor, NXP F8100 PMIC, 3 gigabyte (Gbyte) RAM, 32 Gbyte embedded Multi-Media Controller (eMMC) geheugen, en 64 megabyte (Mbyte) flash geheugen combineert. Samen met het display, de camera en de audio-interfaces, bevat de MEK-kaart een set sensoren die gewoonlijk worden gebruikt in de auto-industrie of in industriële toepassingen. Voor extra connectiviteit, audio en uitbreidingsopties kunnen ontwikkelaars ook de optionele MCIMX8-8X-BB basiskaart van NXP toevoegen.

Conclusie

Voor een groeiend aantal toepassingen zoals automotive, industrie, gebouwenbeheer en HMI's is de verwerkingscapaciteit uitgebreid met zowel de traditionele real-time I/O-verwerking als de opkomende verwerking op applicatieniveau met multimediagrafiek. Hoewel er voor elk type werklast ontwerpopties bestaan, voldoen slechts weinig beschikbare oplossingen aan de groeiende behoefte aan krachtige, energie-efficiënte oplossingen die kunnen voldoen aan de eisen voor veiligheidscertificerende ontwerpen in de auto-industrie en industriële toepassingen.

Zoals blijkt, kunnen ontwikkelaars met behulp van een familie van multicoreprocessors van NXP Semiconductors effectiever ontwerpen implementeren die in staat zijn om aan deze uiteenlopende eisen te voldoen en gemakkelijk op schaal te brengen om te voldoen aan opkomende eisen voor hoge prestaties.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.