Maak snel lage jitter, hoogfrequente klokken met behulp van een vertaallusmodule

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2021-08-04

Ontwerpers van instrumentatie- en meetsystemen hebben behoefte aan signalen met een lage jitter en zonder storingen om de signal-to-noise ratios (SNR's) of error vector magnitudes (EVM's) te kunnen bieden die nodig zijn om te voldoen aan de steeds hogere eisen van de klant. Tegelijkertijd staan zij ook onder grote druk om de printplaatafmetingen, de ontwerpkosten en de complexiteit te beperken. Dit laatste is van cruciaal belang om de ontwikkelingstijd te verkorten en zo tegemoet te komen aan de steeds krapper wordende time-to-market.

Om de vele toepassingsuitdagingen het hoofd te bieden, moeten ingenieurs hun instrumentatie- en meetklokoplossingen omzetten van op maat gemaakte, traditioneel discrete ontwerpen naar meer geïntegreerde oplossingen. Een belangrijke stap in die richting is het gebruik van een geïntegreerde translationele phase-locked loop (PLL). Dit maakt de up-conversie van de frequentie van een traditioneel voltage-controlled oscillatorsignaal (VCO) mogelijk, terwijl de jitter en de faseruis van een vaste externe local oscillator (LO) grotendeels behouden blijven.

Dit artikel bespreekt de rol van vertalingslussen bij het bereiken van de laagste geïntegreerde faseruis in de industrie. Als voorbeeld wordt de ADF4401A translation loop system-in-package (TL SiP) van Analog Devices geïntroduceerd en wordt getoond hoe deze aan de prestatie-eisen voldoet door middel van een uitgangssignaal met sub-10 femtoseconde (fs) rms geïntegreerde breedband jitter-capaciteit en verbeterde isolatie om ongewenste componenten te verzwakken, terwijl tevens wordt voldaan aan de behoeften van ontwerpers op het gebied van integratie, kosten, complexiteit en time-to-market.

Traditionele PLL vs. vertaallusbewerkingen

Het hoofddoel van een translus is het genereren van een uitgangssignaal dat is vergrendeld op een ingangsreferentiesignaal met aanzienlijk verminderde in-band faseruis in vergelijking met traditionele PLL's.

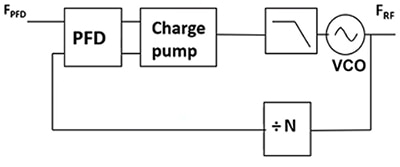

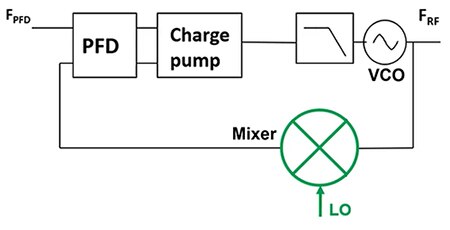

Een standaard PLL bestaat uit een feedbacksysteem met een phase-frequency detector (PFD), een laadpomp, een low-pass filter (LPF), een VCO en een teruggekoppelde frequentiedeler N (Afbeelding 1).

Afbeelding 1: De standaard PLL wordt vergrendeld op een referentie voor een lagere frequentie (FPFD) en genereert een uitgangsfrequentie (FRF). (Bron afbeelding: Bonnie Baker)

Afbeelding 1: De standaard PLL wordt vergrendeld op een referentie voor een lagere frequentie (FPFD) en genereert een uitgangsfrequentie (FRF). (Bron afbeelding: Bonnie Baker)

De PFD vergelijkt de fase van de ingangsreferentie en de fase van het feedbacksignaal en genereert een reeks pulsen die evenredig zijn met de fasefout tussen beide. De laadpomp ontvangt de PFD-impulsen en zet ze om in stroombron- of - sinkpulsen die op hun beurt de VCO in frequentie naar boven of beneden afstellen. De LPF verwijdert alle hoogfrequente energie van de pulsen en zet ze om in een spanning die de VCO kan gebruiken. Het uitgangssignaal van de VCO wordt via de N-deler teruggevoerd naar het PFD-blok om de lus te voltooien.

De frequentieoverdrachtsfunctie van figuur 1 wordt berekend met behulp van vergelijking 1:

![]() Vergelijking 1

Vergelijking 1

Waarbij FRF de uitgangsfrequentie is

N is de verhouding van de teruggekoppelde deler (kan geheel of gebroken zijn)

FPFD is de PFD-frequentie

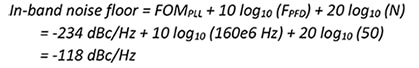

De in-band ruisvloer van Afbeelding 1 wordt berekend met behulp van vergelijking 2:

![]() Vergelijking 2

Vergelijking 2

Waarin FOMPLL het in-band faseruis-ondergrenscijfer (FOM) van de PLL is

Neem een voorbeeld met een in-band faseruisvloer FOM van -234 decibel per Hertz (dB/Hz); een PFD-frequentie (FPFD) van 160 megahertz (MHz), en een uitgangsfrequentie (FRF) van 8 gigahertz (GHz).

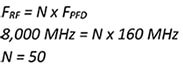

Voor dit systeem wordt vergelijking 1 gebruikt om de waarde van N te berekenen:

Vergelijking 2 wordt gebruikt om de in-band ruisvloer te berekenen:

In de bovenstaande berekening draagt de N-deler sterk bij tot de totale in-band ruisvloer, met 20 log10 (50), gelijk aan 34 dB. Een kleinere N-waarde verlaagt de in-band ruisvloer, maar verlaagt ook de uitgangsfrequentie. Dus hoe kunnen we een hoge uitgangsfrequentie genereren en een lagere lusversterking (N) behouden?

Afbeelding 2: Voor een standaard PLL in dit voorbeeld heeft de ruis van de terugkoppelingsdeler (20 log10(N)) een 34 dB hogere in-band ruis vergeleken met het onderste gele diagram waar N = 1. (Bron afbeelding: Bonnie Baker)

Afbeelding 2: Voor een standaard PLL in dit voorbeeld heeft de ruis van de terugkoppelingsdeler (20 log10(N)) een 34 dB hogere in-band ruis vergeleken met het onderste gele diagram waar N = 1. (Bron afbeelding: Bonnie Baker)

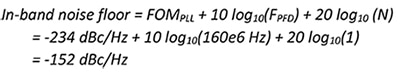

De oplossing voor dit probleem is de N-verdeler te vervangen door een down-converterende mengtrap (Afbeelding 3).

Afbeelding 3: Een conversielus gebruikt een mixer om de VCO-frequentie te down-converteren naar de PFD-frequentie in plaats van een traditionele feedback-deler te gebruiken. (Bron afbeelding: Bonnie Baker)

Afbeelding 3: Een conversielus gebruikt een mixer om de VCO-frequentie te down-converteren naar de PFD-frequentie in plaats van een traditionele feedback-deler te gebruiken. (Bron afbeelding: Bonnie Baker)

In Afbeelding 3 vervangt de mixer de teruggekoppelde N-deler, hetgeen resulteert in een lusversterking gelijk aan 1 (N=1). Hierdoor wordt de bijdrage van de terugkoppellus aan de in-band ruisvloer sterk verminderd. Voor de berekening van de in-band ruis is de waarde van N nu gelijk aan 1. Met behulp van vergelijking 2 is de in-band ruisvloer voor het gewijzigde systeem als volgt:

De nieuwe in-band ruis vertoont een verbetering van 34 dBc/Hz.

In Afbeelding 3 is de mixer afhankelijk van een LO met zeer weinig ruis, de zogenaamde Offset LO. FLO ±FRF moet gelijk zijn aanFPFD om vergrendeling te bereiken.

Met de vertaallus-architectuur is de faseruis van de Offset LO zeer belangrijk om de beste prestaties aan de RF-uitgang te bereiken. Daarom ontwerpen ingenieurs gewoonlijk een Offset LO op basis van spanningsgestuurde surface acoustic wave (SAW), of oscillators (VCSOs, of kamgeneratores, of dielectric resonator oscillators (DRO's). OPMERKING: Neem contact op met Analog Devices voor ondersteuning bij het ontwerpen van een Offset LO.

Uitdagingen van de vertaallus

Traditioneel impliceert het ontwerp van een vertalingslus met lage ruis de implementatie van talrijke circuitblokken, wat resulteert in een complex ontwerp, meestal groot, en met beperkte flexibiliteit. Bovendien moet de gehele schakeling worden gevalideerd en gekarakteriseerd voor de beoogde werking. Een belangrijk punt van zorg bij het ontwerp is bijvoorbeeld LO-lekkage (LO naar RF-isolatie) naar het RF-uitgangssignaal. Dit is een belangrijke uitdaging voor ingenieurs om aan te pakken. Bij traditionele ontwerpen gaan ingenieurs gewoonlijk over tot meerdere ontwerpiteraties om optimale prestaties en geschikte isolatie te bereiken.

Afbeelding 3 toont hoe de ADF4401A belangrijke circuitblokken integreert om een volledig gekarakteriseerde oplossing te bieden en de traditioneel moeilijke gebieden elimineert met betrekking tot de prestaties en de isolatie in vertaallus-ontwerpen. Met deze programmeerbare oplossing kunnen ingenieurs al bij de eerste poging optimale prestaties bereiken en de tijd tot de marktintroductie verkorten.

Evaluatie van de ADF4401A

De ADF4401A is ontworpen om ingenieurs te helpen de doorlooptijd van hoogwaardige instrumentatie te verkorten, door gebruik te maken van een oplossing voor frequentiegeneratie met een RF-bandbreedte van 62,5 MHz tot 8 GHz. Door gebruik te maken van een down-converterende mixer, heeft de ADF4401A een zeer lage in-band ruis met een breedband jitter van ~9 femtoseconden (fs) geïntegreerd van 100 Hz tot 100 MHz. De ontwerp- en lay-outtechnieken in de ADF4401A maken een typisch storingsvrij dynamisch bereik van 90 dBc mogelijk. Een pakketgrootte van 18 x 18 x 2,018 millimeter (mm) vermindert de ruimte op printplaten aanzienlijk in vergelijking met een traditioneel discreet ontwerp.

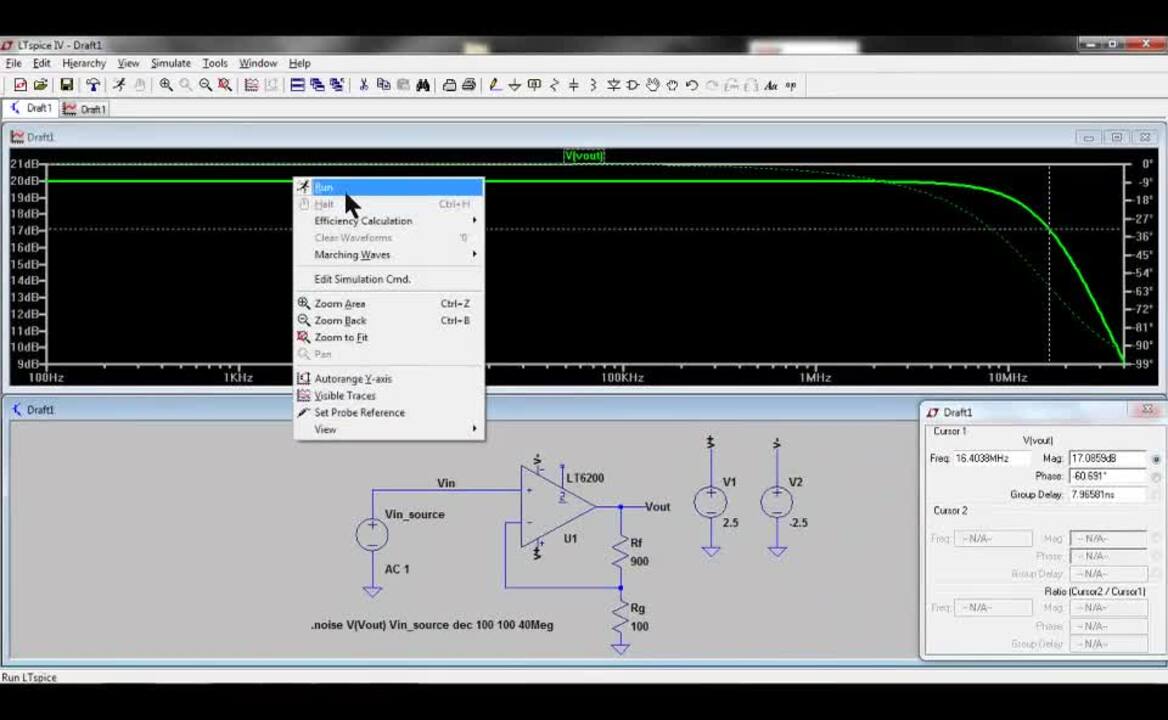

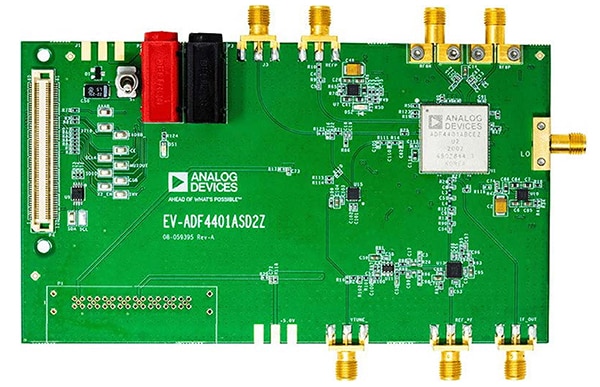

Om de prestaties van het apparaat te evalueren, kunnen ontwerpers gebruik maken van het EV-ADF4401ASD2Z evaluatiebord (Afbeelding 4). De kaart bevat een complete conversielus, inclusief een externe PFD (HMC3716), een actief filter (LT6200), en een multiplexer (ADG1609).

Afbeelding 4: Het EV-ADF4401ASD2Z-evaluatiebord voor de ADF4401A-vertaallusmodule bevat een externe PFD, een USB-interface en spanningsregelaars. (Bron afbeelding: Analog Devices)

Afbeelding 4: Het EV-ADF4401ASD2Z-evaluatiebord voor de ADF4401A-vertaallusmodule bevat een externe PFD, een USB-interface en spanningsregelaars. (Bron afbeelding: Analog Devices)

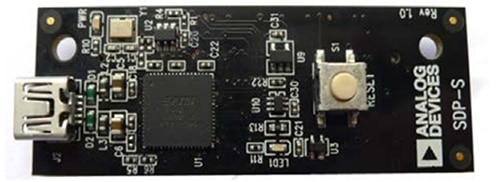

De EV-ADF4401ASD2Z omvat de ADF4401A TL SiP met geïntegreerde VCO, een lusfilter (5 MHz), een PFD, een USB-interface en spanningsregelaars. Bovendien vereist de EV-ADF4401ASD2Z de EVAL-SDP-CS1Z (SDP-S) systeemdemonstratieplatform (SDP) (serieel) besturingskaart (Afbeelding 5). Het bord voorziet in een USB-verbinding van een PC naar de EV-ADF4401ASD2Z zodat deze kan worden geprogrammeerd. De besturingskaart wordt niet meegeleverd in de EV-ADF4401ASD2Z kit.

Afbeelding 5: Het EVAL-SDP-CS1Z (of SDP-S) controllerbord is nodig voor een USB-verbinding van de EV-ADF4401ASD2Z naar een PC om te programmeren. (Bron afbeelding: Analog Devices)

Afbeelding 5: Het EVAL-SDP-CS1Z (of SDP-S) controllerbord is nodig voor een USB-verbinding van de EV-ADF4401ASD2Z naar een PC om te programmeren. (Bron afbeelding: Analog Devices)

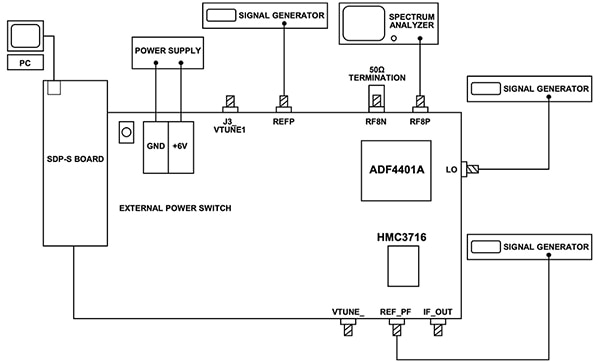

Afbeelding 6 toont de fysieke aansluitingen van het EV-ADF4401ASD2Z-systeem. De bijbehorende Analyse | Controle | Evaluatie (ACE) software bestuurt de TL SiP functies. De voeding is afkomstig van een extern aangebrachte 6-volt voeding.

Afbeelding 6: Een EV-ADF4401ASD2Z-opstellingsschema toont de apparatuur en aansluitingen die nodig zijn om de ADF4401A te evalueren, waaronder de SDP-S bedieningskaart, PC, voeding, signaalgeneratoren en spectrumanalyzer. (Bron afbeelding: Analog Devices)

Afbeelding 6: Een EV-ADF4401ASD2Z-opstellingsschema toont de apparatuur en aansluitingen die nodig zijn om de ADF4401A te evalueren, waaronder de SDP-S bedieningskaart, PC, voeding, signaalgeneratoren en spectrumanalyzer. (Bron afbeelding: Analog Devices)

De aanbevolen apparatuur voor gebruik met dit evaluatiebord omvat een Windows PC, een spectrum analyzer of een signaalbron analyser en drie signaalgenerators.

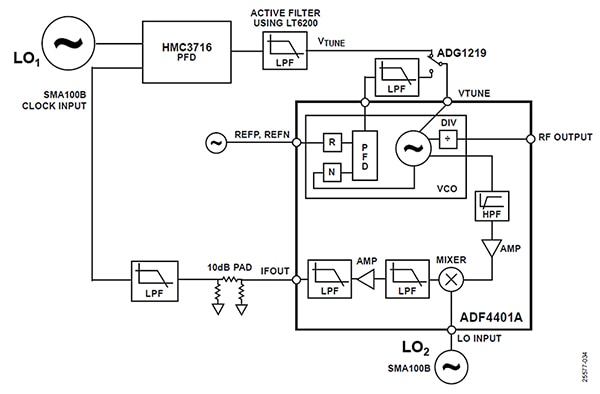

Het blokschema van de EV-ADF4401ASD2Z toont de ADF4401A module, samen met de HMC3716 PFD van Analog Devices, de LT6200 op-amp en de ADG1219 SPDT-switch (Afbeelding 7).

Afbeelding 7: Het blokschema van het EV-ADF4401ASD2Z-evaluatiebord toont de belangrijkste componenten die de AD4401A-vertaallus ondersteunen. (Bron afbeelding: Analog Devices)

Afbeelding 7: Het blokschema van het EV-ADF4401ASD2Z-evaluatiebord toont de belangrijkste componenten die de AD4401A-vertaallus ondersteunen. (Bron afbeelding: Analog Devices)

Het is van vitaal belang een PFD te gebruiken die bij hoge frequenties kan werken, aangezien dit de behoefte aan delers, die de in-band ruisrespons kunnen verslechteren, tot een minimum beperkt. De 1,3 GHz fasevergelijkingsfrequentie van de Analog Devices HMC3716 maakt hem ideaal voor gebruik in het IF-bereik van de ADF4401A. Doordat een dergelijke schakeling zowel frequentie als fase kan vergelijken, zijn er geen extra schakelingen nodig om de frequentie te sturen naar de beoogde uitgangsfrequentie. De HMC3716 wordt de externe PFD om de offset-lus te voltooien. Het hoogfrequente werkingsbereik en de ultralage faseruisvloer van de HMC3716 maken het mogelijk om lusfilters met een grote bandbreedte te ontwerpen.

In Afbeelding 7 dempt de LT6200 op-amp met een LPF-configuratie de hoogfrequente spurs, terwijl de ADG1219-switch de vertaallus van het systeem completeert.

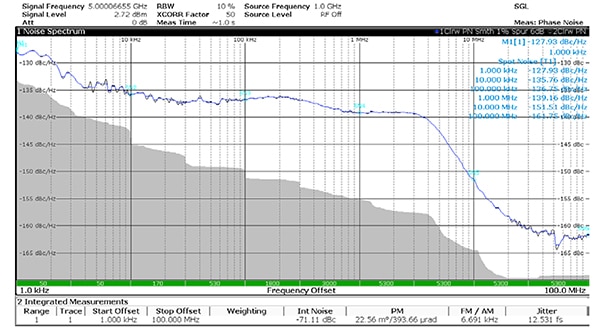

De EV-ADF4401ASD2Z-evaluatie-opstelling maakt in-band ruisplots en jitter-metingen zoals getoond in Afbeelding 8.

Afbeelding 8: Enkelzijbandige faseruis bij 5 GHz uitgang, met een externe HMC3716 referentie van 500 MHz en externe LO op 4,5 GHz. (Bron afbeelding: Analog Devices)

Afbeelding 8: Enkelzijbandige faseruis bij 5 GHz uitgang, met een externe HMC3716 referentie van 500 MHz en externe LO op 4,5 GHz. (Bron afbeelding: Analog Devices)

In Afbeelding 8 is de LO2- en HMC3716-ingang een SMA100B RF- en microgolfsignaalgenerator. De LO2 in-band ruis van de evaluatiekaart is ongeveer -135 dBc/Hz, wat duidelijk is bij lage offsets tot 300 kHz. De LO2, de ADF4401A-module, de HMC3716 PFD en het lusfilter dragen bij tot een in-band ruis van ongeveer -140 dBc/Hz. De interne faseruis verschijnt tussen 5 MHz en 50 MHz, en de faseruisvloer van de armatuur is ongeveer -160 dBc/Hz. Samen geven deze een rms jitter van 12,53 fs in totaal.

Conclusie

Snelle instrumentatiesystemen vereisen klokken met een extreem lage jitter om ervoor te zorgen dat de uitgangsgegevens onaangetast blijven. De uitdaging voor ingenieurs bestaat erin geschikte apparatuur te vinden waarmee het hogesnelheids gigahertz-kloksysteem kan worden gebouwd. De ADF4401A-vertaallus vereenvoudigt de apparaatkeuze voor de bouw van het kloksysteem aanzienlijk, en biedt een compacte module die lage jitter bij hogere frequenties garandeert, en tegelijkertijd de ruimte op de printplaat, de kosten en de tijd om op de markt te komen beperkt.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.