De grondbeginselen van fasevergrendelde lusfrequentiesynthesizers

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2021-02-03

Stijgende datasnelheden in hoge-snelheid seriële communicatiebussen vereisen systeemklokken met hogere frequenties, superieure stabiliteit, grotere frequentieresolutie en hogere signaalzuiverheid. Directe digitale synthesizers bieden deze kenmerken, maar alleen bij frequenties onder 2 of 3 gigahertz (GHz). Er is een oplossing nodig voor frequenties tot tientallen gigahertz.

Deze oplossing begint met op fasevergrendelde lus (PLL) gebaseerde analoge frequentiesynthesizers die klokfrequenties tot 30 GHz genereren. Integer N-synthesizers (die de referentiefrequentie vermenigvuldigen met een gehele waarde) en fractionele N synthesizers (die de referentiefrequentie vermenigvuldigen met niet-integere fractionele waarden) maken gebruik van speciale technieken om faseruis en soortgelijke signaalonzuiverheden te minimaliseren.

Dit artikel beschrijft het ontwerp van zowel integer als fractionele N-frequentiesynthesizers aan de hand van voorbeeldapparaten van Analog Devices. In het artikel worden ook de innovaties belicht waardoor deze toestellen kunnen worden gebruikt voor seriële hogesnelheidsdatalinks en voor frequency agile radars.

Integer N fase-gesloten lus synthesizers

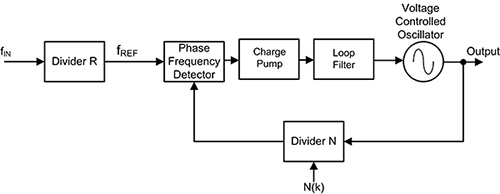

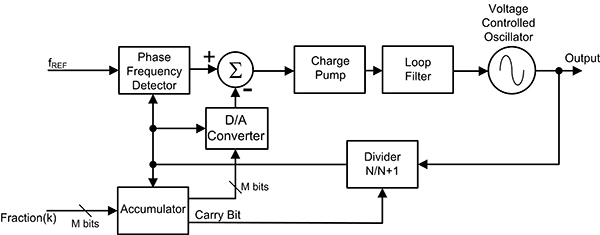

PLL-circuits worden gebruikt voor frequentie- en faseregeling. Zij kunnen worden geconfigureerd als klokbronnen, frequentievermenigvuldigers, demodulators, tracking-generators of klokterugwinningscircuits. Elk van deze toepassingen vereist andere kenmerken, maar zij maken alle gebruik van hetzelfde basisconcept voor de schakeling. Afbeelding 1 toont een blokschema van een basis PLL die geconfigureerd is als een frequentievermenigvuldiger.

Afbeelding 1: Blokschema van een klassieke integer N fasevergrendelde lusfrequentiesynthesizer (Bron afbeelding: DigiKey)

Afbeelding 1: Blokschema van een klassieke integer N fasevergrendelde lusfrequentiesynthesizer (Bron afbeelding: DigiKey)

De werking van dit circuit is typerend voor alle fasevergrendelde lussen. Het is in feite een terugkoppelingsregelsysteem dat de fase van een spanningsgestuurde oscillator (VCO) regelt. Het ingangssignaal wordt toegepast op een voorschaaldeler, die de ingangsfrequentie deelt door een factor R. De uitgang van de voorschaler is de referentiefrequentie, die een ingang vormt voor een fase-frequentiedetector (PFD).

De andere PFD-ingang is een feedbacksignaal van de uitgang van een deler-door-N-teller. Normaal gesproken, als de PLL is vergrendeld, zullen de frequenties van beide signalen bijna hetzelfde zijn. De uitgang van de fasedetector is een spanning die evenredig is met het faseverschil tussen de twee ingangen. Als de lus ontgrendeld is, zoals gebeurt bij het opstarten, of als er een grote momentane verschuiving is in de frequentie van de ingang, dan werkt de fase-frequentiedetector om de PLL-werkfrequentie naar de gewenste instelling te sturen. Wanneer die frequentie is bereikt, keert de PFD terug naar de fasedetectormodus en heeft een uitgang die evenredig is met het faseverschil tussen de referentiefrequentie en het feedbacksignaal.

De fasefrequentiedetector drijft een laadpomp aan, die een bipolair geschakelde stroombron is. Dit betekent dat het positieve en negatieve stroompulsen kan afgeven aan het lusfilter van de PLL.

Het lusfilter egaliseert het fasefoutsignaal en bepaalt tevens de dynamische kenmerken van de PLL. Het gefilterde signaal regelt de VCO. Merk op dat de uitgang van de VCO een frequentie heeft die N maal zo groot is als de ingang van de frequentiereferentie-ingang van de fasefrequentiedetector en N/R maal zo groot is als de frequentie-ingang. Dit uitgangssignaal wordt teruggestuurd naar de fasedetector via de gedeeld-door-N-teller.

Gewoonlijk wordt het lusfilter zo ontworpen dat het bij de kenmerken past die nodig zijn voor de toepassing van de PLL. Als de PLL dient voor het verwerven en traceren van een signaal, is de bandbreedte van het lusfilter groter dan als de PLL een vaste ingangsfrequentie zou verwachten. Het frequentiebereik dat de PLL accepteert en waarop ze kan locken, wordt het "vangbereik" genoemd Zodra de PLL gelocked is en een signaal volgt, wordt het bereik van de frequenties die de PLL zal volgen, het "volgbereik" genoemd Gewoonlijk is het volgbereik groter dan het vangbereik. Het PLL-lusfilter bepaalt ook hoe snel de signaalfrequentie kan veranderen en toch een lock kan behouden - d.w.z. de maximale slew rate. Hoe nauwer de bandbreedte van het lusfilter, hoe kleiner de bereikbare fasefout. Dit gaat wel ten koste van een langzamere reactie en een verminderd vangbereik. PLL's die worden gebruikt in kloktoepassingen werken voornamelijk met vaste frequenties. In het algemeen moet de bandbreedte van het lusfilter veel kleiner zijn dan de referentiefrequentie.

Aangezien de PLL-uitgangsfrequentie een geheel veelvoud is van de referentiefrequentie, is de frequentieresolutie gelijk aan de referentiefrequentie. Om een fijnere frequentieresolutie te verkrijgen moet de referentiefrequentie worden verlaagd, hetgeen wordt gedaan met de voorschaalteller R.

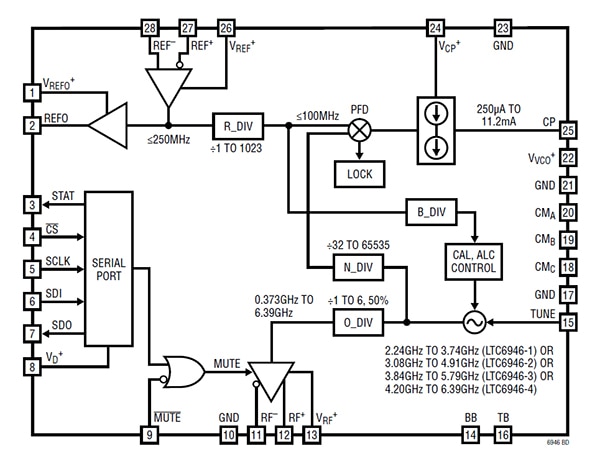

Een commercieel voorbeeld van een integer N-frequentiesynthesizer is de LTC6946IUFD-3#PBF van Analog Devices, een ruisarme 0,64 tot 5,790 GHz synthesizer met een geïntegreerde VCO en uitstekende spurious-prestaties (Afbeelding 2). Het maakt deel uit van een familie van vier synthesizer-IC's, elk met een verschillend frequentiebereik, dat een totaal bereik van 0,373 tot 6,390 GHz bestrijkt.

Afbeelding 2: Het blokschema van de Analog Devices LTC6946IUFD-3#PBF integer N frequentiesynthesizer met geïntegreerde VCO. (Bron afbeelding: Analog Devices)

Afbeelding 2: Het blokschema van de Analog Devices LTC6946IUFD-3#PBF integer N frequentiesynthesizer met geïntegreerde VCO. (Bron afbeelding: Analog Devices)

Deze synthesizer vereist een extern, door de gebruiker geleverd lusfilter, dat kan worden geoptimaliseerd voor de specifieke toepassing. Er is een interne pre-scale tellerdeler met een verdeelbereik van 1 tot 1023. De lusdeler heeft een bereik van 32 tot 65535. De laadpompstroom is instelbaar van 250 microampère (mA) tot 11,2 milliampère (mA) om te voldoen aan de eisen van het lusfilter.

Fractionele N-fasevergrendelde lus-synthesizers

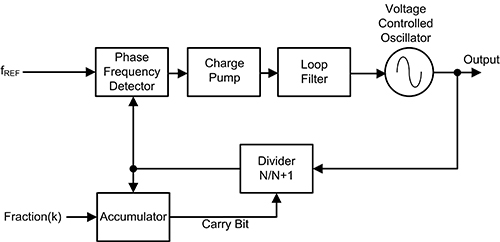

De frequentieresolutie van de PLL-synthesizer kan worden verbeterd door de stapgrootte te verkleinen tot minder dan gehele waarden - d.w.z. door fractionele stappen te maken in de lusdeler (N). Dit wordt bereikt door de aftelwaarde dynamisch te variëren of te "ditheren". Dit betekent dat de delerinstelling de waarde N vasthoudt voor een vast aantal cycli van de PLL-uitgangsfrequentie en periodiek wordt getrapt naar een andere waarde, zoals N+1. Bijvoorbeeld, als de delerinstelling 4 is voor drie referentieperioden en 5 voor de vierde referentiecyclus, dan is de effectieve aftelling 4,25. Een manier om dit te bereiken is door gebruik te maken van een accumulator zoals afgebeeld in Afbeelding 3.

Afbeelding 3: Het blokschema van een fractionele N PLL-synthesizer die gebruik maakt van een accumulator om de deler-telling te moduleren. (Bron afbeelding: DigiKey)

Afbeelding 3: Het blokschema van een fractionele N PLL-synthesizer die gebruik maakt van een accumulator om de deler-telling te moduleren. (Bron afbeelding: DigiKey)

De accumulator telt de uitgangsimpulsen van de deler, en elke M, waarbij M de modulus van de accumulator is, geeft hij een carry-bit af dat de ingang van de deler verandert. Afbeelding 4 gaat verder met het voorbeeld van een fractionele delerinstelling van 4,25.

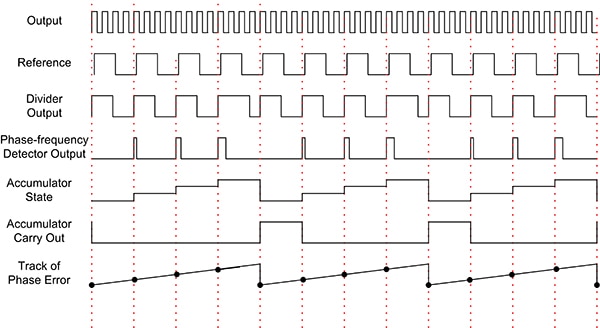

Afbeelding 4: Tijdschema voor een fractionele N-synthesizer met behulp van een accumulator. (Bron afbeelding: DigiKey)

Afbeelding 4: Tijdschema voor een fractionele N-synthesizer met behulp van een accumulator. (Bron afbeelding: DigiKey)

De accumulator wordt aangestuurd door de verdeelde uitgang en telt modulo vier, d.w.z. dat M gelijk is aan vier. Elke vierde puls genereert een carry-uitgang, die het getal van de deler met één verhoogt. De accumulator wordt gereset en begint opnieuw te tellen. De toename van de delerinstelling verschuift de uitgangsfrequentie, wat resulteert in een geaccumuleerde fase-offsetfout. Het spoor van de fasefout toont de pulswaarde als functie van de tijd.

De gemiddelde delerinstelling is 4,25, maar de uitgang van de synthesizer is fasemodulerend, wat resulteert in valse tonen in de uitgang. Als we naar de toestand van de accumulator kijken, is het duidelijk dat deze de fasefout volgt. Dit kan worden gebruikt om de modulatie te verwijderen, zoals getoond in Afbeelding 5.

Afbeelding 5: Gebruik van de D/A geconverteerde accumulatortoestand om de fasemodulatie ten gevolge van de fractionele N dithering op te heffen. (Bron afbeelding: DigiKey)

Afbeelding 5: Gebruik van de D/A geconverteerde accumulatortoestand om de fasemodulatie ten gevolge van de fractionele N dithering op te heffen. (Bron afbeelding: DigiKey)

De toestand van de accumulator wordt omgezet in analoog door een digitaal-naar-analoog-convertor (D/A) en geschaald en afgetrokken van de uitgang van de fasefrequentiedetector om de fasemodulatie ten gevolge van de fractionele N dithering te elimineren. Dit moet met grote zorg gebeuren; als het correctiesignaal niet precies overeenkomt met de fasefout, zullen valse tonen aan de uitgang het gevolg zijn.

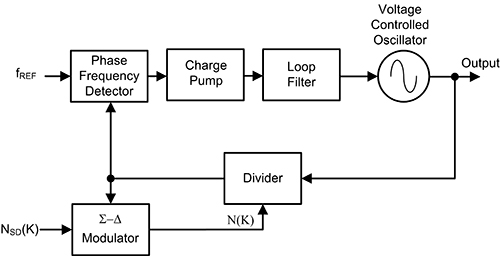

Voer de sigma-delta modulator in

De periodiciteit in de accumulator is de oorzaak van valse outputs van de synthesizer. Indien de accumulator wordt vervangen door een sigma-delta modulator, dan kunnen digitale technieken worden toegepast om de deler-telling zodanig te moduleren dat de ongewenste reacties en de ruis tot een minimum worden beperkt. Deze vervanging is afgebeeld in Afbeelding 6.

Afbeelding 6: Vervanging van de accumulator door een sigma-delta modulator maakt het mogelijk digitale technieken toe te passen om het aantal delers te variëren en zo de spurious-responses te beperken. (Bron afbeelding: DigiKey)

Afbeelding 6: Vervanging van de accumulator door een sigma-delta modulator maakt het mogelijk digitale technieken toe te passen om het aantal delers te variëren en zo de spurious-responses te beperken. (Bron afbeelding: DigiKey)

Er zijn eigenlijk twee gangbare digitale technieken die worden toegepast in de sigma-delta modulatietopologie. De eerste methode houdt in dat het aantal tellingen van de deler N over een groter bereik van waarden wordt verhoogd, zodat de gemiddelde delingsfactor de gewenste fractionele delerwaarde oplevert. Dit zal de primaire fractionele uitlopers verminderen. De accumulator-gebaseerde synthesizer varieert de telling tussen twee toestanden. Dit is een eerste orde modulatie methode. Een sigma-delta fractionele PLL van de n-de orde moduleert de N-teller tussen 2n verschillende waarden. Zo zou een derde-orde modulator afwisselend acht verschillende delerwaarden gebruiken, en een vierde-orde modulator 16 verschillende delerwaarden.

De tweede digitale techniek - ook wel dithering genoemd - houdt in dat de 2N-sequentie zodanig wordt gerandomiseerd dat zij pseudorandom is. Terwijl een gemiddelde fractionele delerverhouding wordt gehandhaafd, worden de fractionele sporen omgezet in gevormde willekeurige ruis op een zodanige wijze dat deze door de PLL kan worden gefilterd.

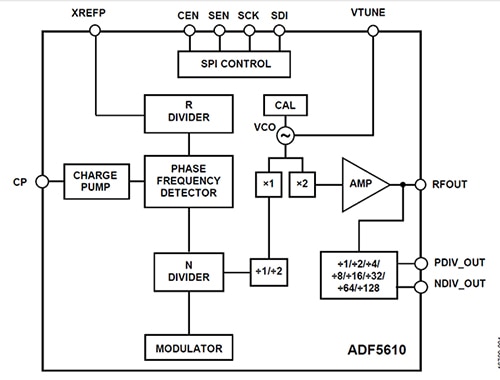

Een commerciële versie van een sigma-delta fractionele N-synthesizer is de Analog Devices ADF5610BCCZ, een ruisarme 0,57 megahertz (MHz) tot 14,6 GHz fractionele N-synthesizer met een geïntegreerde VCO (Afbeelding 7).

Afbeelding 7: Een blokschema van de Analog Devices ADF5610BCCZ die zowel fractionele N als integer synthesizerconfiguraties ondersteunt. (Bron afbeelding: Analog Devices)

Afbeelding 7: Een blokschema van de Analog Devices ADF5610BCCZ die zowel fractionele N als integer synthesizerconfiguraties ondersteunt. (Bron afbeelding: Analog Devices)

De ADF5610 heeft een externe referentie-oscillator en lusfilter nodig. Het heeft een geïntegreerde VCO met een fundamentele frequentie van 3650 MHz tot 7300 MHz. Deze frequenties worden intern verdubbeld en gerouteerd naar de RFOUT-pen. Er is een differentiële uitgang waarmee de verdubbelde VCO-frequentie kan worden gedeeld door factoren van 1, 2, 4, 8, 16, 32, 64, of 128, waardoor RF-uitgangsfrequenties tot 57 MHz kunnen worden gegenereerd.

De ADF5610 maakt gebruik van een geavanceerde sigma-delta modulator met een 24-bit fractionele modulus die uitzonderlijk lage spurious-niveaus bereikt. Zoals in alle synthesizers die gebruik maken van een sigma-delta modulator, maakt dit toestel gebruik van digitale signaalverwerkingstechnieken om de gewenste gemiddelde fractionele deler verhouding te vinden. Dit proces, geklokt op de PFD-snelheid, produceert outputmodulatieruis, kwantisatieruis genaamd, met een hoogdoorlaat-frequentierespons. Het externe laagdoorlaat lusfilter wordt gebruikt om deze kwantiseringsruis te filteren tot een niveau onder de faseruis van de VCO, waardoor wordt voorkomen dat de ruis bijdraagt tot de totale faseruis van het systeem.

De ADF5610 heeft ook een exacte frequentiemodus voor een frequentiefout van 0 hertz (Hz). In deze modus kunnen exacte frequenties worden gegenereerd tussen aangrenzende gehele N grensstappen, terwijl toch de volledige 24-bits faseaccumulatormodulus wordt gebruikt. Hiermee worden exacte frequentiestappen bereikt met een hoge vergelijkingssnelheid van de fasedetector, waardoor de PLL in deze modus uitstekende prestaties op het gebied van faseruis en spurious kan blijven leveren.

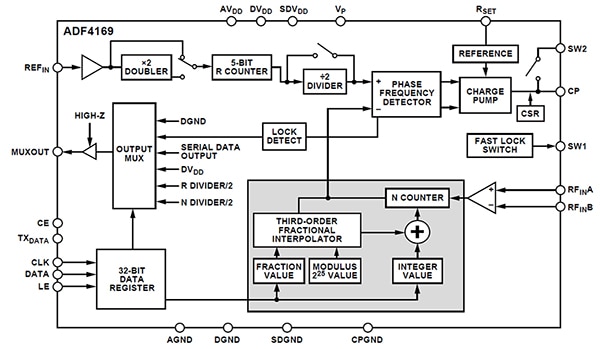

De Analog Devices ADF4169CCPZ-RL7 is een andere PLL-synthesizer die kan worden geconfigureerd als een integer N- of een fractioneel N-apparaat. Hij werkt met een RF-bandbreedte tot 13,5 GHz met modulatie en golfvormgeneratie. Hij maakt gebruik van een externe referentiefrequentie-ingang, VCO en lusfilter. Het heeft een derde-orde sigma-delta modulator voor fractionele N synthese die kan worden uitgeschakeld, zodat het apparaat in integer N modus kan werken (Afbeelding 8).

Afbeelding 8: De Analog Devices ADF4169CCPZ-RL7 maakt gebruik van een derde-orde sigma-delta modulator. (Bron afbeelding: Analog Devices)

Afbeelding 8: De Analog Devices ADF4169CCPZ-RL7 maakt gebruik van een derde-orde sigma-delta modulator. (Bron afbeelding: Analog Devices)

De ADF4158WCCPZ-RL7 synthesizer is bestemd voor gebruik in frequentiegemoduleerde continue-golfradars (FMCW). Hij is geschikt voor verschillende soorten gemoduleerde golfvormen in het frequentiedomein, waaronder zaagtand- en driehoekige integrators. Dit is een speciale eigenschap die nodig is bij radartoepassingen.

Conclusie

De stijgende datasnelheden in seriële communicatiebussen met hoge snelheid dwingen ontwerpers verder te kijken dan directe digitale synthesizers - die het best werken onder 3 GHz - voor systeemklokoplossingen. PLL-gebaseerde frequentiesynthesizers die gebruik maken van integer N en fractional N topologieën leveren stabiele signalen met weinig ruis voor hoogfrequente klok-, seriële datacommunicatie- en radartoepassingen voor frequenties tot tientallen gigahertz.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.