Gebruik een enkele ultra-low-power HMP-processor voor zowel realtime als applicatieverwerkingstaken

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2019-08-06

Consumenten verwachten van persoonlijke elektronica en andere mobiele apparaten zowel een snellere respons als verbeterde functionaliteit — en tegelijkertijd een langere levensduur van de batterij. Deze vereisten voor realtime respons én hoge prestaties in veel toepassingen dwingen ontwikkelaars om afzonderlijke processors te gebruiken om aan deze tegenstrijdige behoeften te voldoen. Dit brengt echter kosten met zich mee en vereist meer vermogen en geheugenruimte, evenals andere eisen voor hardware-layout en softwarecomplexiteit.

Een betere aanpak zou zijn om de vereiste hardware in één enkele chip te integreren. En dit is waar heterogene multicore-processors (HMP) van pas komen. Deze processors bevatten meerdere processorkernen van verschillende typen en bieden voordelen zoals prestatie-optimalisatie, lager stroomverbruik en verbeterde systeembeveiliging en betrouwbaarheid.

Dit artikel beschrijft hoe ontwikkelaars een heterogene multicore-processor van NXP Semiconductors kunnen gebruiken om aan de vraag naar deze gemengde werklasten te voldoen zonder afbreuk te doen aan de vereisten voor laag stroomgebruik en eenvoudig ontwerp.

Veranderende eisen

Vooruitgang in sensortechnologie en gegevensverwerkingsalgoritmes heeft voor ontwikkelaars aanzienlijke mogelijkheden gecreëerd om aan de tegenstrijdige eisen voor realtime gegevensverzameling en rekenintensieve algoritmes te voldoen. In het verleden verdeelden ontwikkelaars deze taken doorgaans over afzonderlijke systemen.

Op het laagste niveau van de netwerkhiërarchie zouden geïntegreerde processors, zoals die gebaseerd op de Arm® Cortex®-M4-kern, gegevens verzamelen en geoptimaliseerde code uitvoeren op een realtime besturingssysteem (RTOS) of een bare-metal systeem. Op een hoger niveau binnen de hiërarchie zouden krachtige applicatieprocessors, zoals die gebaseerd op de Arm Cortex-A7-kern, op hun beurt gegevensanalyse-algoritmes uitvoeren, waarbij applicatiecode wordt uitgevoerd op vertrouwde besturingssystemen zoals Linux of Android.

De opkomst van edge computing-systemen heeft de uitvoering van applicatiecode dichter bij de gegevensbron gebracht. In feite heeft de vraag naar een snellere respons van complexere analyse-algoritmes de verantwoordelijkheid voor applicatieverwerking bij de eindapparaten zelf gelegd. Consumenten verwachten in toenemende mate dat geavanceerde analysemogelijkheden, zoals kunstmatige intelligentie, geïntegreerd zijn in apparaten zoals Internet of Things (IoT)-sensoren, wearables en andere low-power producten.

De rol van heterogene multicore-verwerking

Dankzij de opkomst van HMP-processors die geïntegreerde kernen en applicatieverwerkingskernen combineren, kunnen ontwikkelaars gemengde taken in veel toepassingen efficiënter aan. HMP-processors integreren verschillende kernen, elk geoptimaliseerd voor de individuele taakeisen van het doelproduct. Met de NXP i.MX 7ULP (ultra-low-power) processorfamilie kunnen ontwikkelaars de prestatiecapaciteiten van een HMP-architectuur benutten om te voldoen aan de compromisloze vraag van consumenten naar hoge prestaties en een lange levensduur van de batterij in ULP-producten van de volgende generatie.

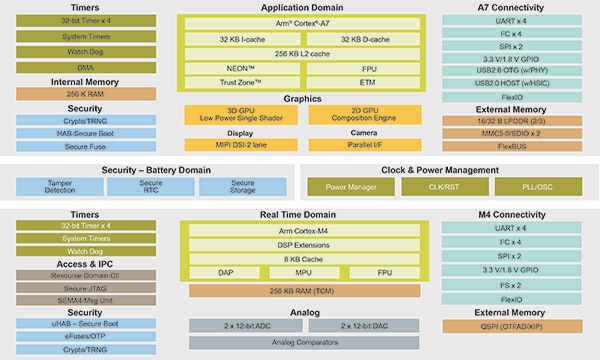

De i.MX 7ULP-processors zijn verkrijgbaar in verschillende versies, zowel voor consumentenproducten (MCIMX7U5DVP07SC) als industriële toepassingen (MCIMX7U5CVP06SC) en integreren heterogene kernen met grafische verwerkingseenheden (GPU’s), beveiligingsaccelerators, geheugencontrollers en een volledige set randapparatuurinterfaces (Afbeelding 1).

Afbeelding 1: De NXP i.MX 7ULP-applicatieprocessors combineren een Arm Cortex-M4-kern voor real-time verwerking en een Arm Cortex-A7-kern voor de verwerking van applicaties, samen met een uitgebreid assortiment van modules en randapparatuur. Afzonderlijke powerdomeinen zorgen voor optimalisatie van stroomgebruik en prestaties. (Bron: NXP)

Afbeelding 1: De NXP i.MX 7ULP-applicatieprocessors combineren een Arm Cortex-M4-kern voor real-time verwerking en een Arm Cortex-A7-kern voor de verwerking van applicaties, samen met een uitgebreid assortiment van modules en randapparatuur. Afzonderlijke powerdomeinen zorgen voor optimalisatie van stroomgebruik en prestaties. (Bron: NXP)

De NXP i.MX 7ULP-familie is speciaal ontworpen voor draagbare ontwerpen met beperkt stroomgebruik en komt tegemoet aan nieuwe behoeften door een Arm Cortex-A7-kern en een Cortex-M4-kern te combineren, elk gevoed door een afzonderlijk powerdomein. Bovendien wordt gebruik gemaakt van zogenaamde ‘powereilanden’ om verschillende modules selectief uit te schakelen wanneer ze niet nodig zijn. Zoals hieronder wordt beschreven, kunnen ontwikkelaars, dankzij de in i.MX 7ULP-processors geïntegreerde geavanceerde powermanagementfuncties, deze powerdomeinen en powereilanden gebruiken om prestaties en stroomgebruik af te stemmen op hun toepassingen.

Optimaliseren van stroomgebruik

NXP heeft bij het ontwerp van de i.MX 7ULP-familie functies voor optimalisatie van stroomgebruik en prestaties ingebouwd, in zowel het chipontwerp als de gehele architectuur.

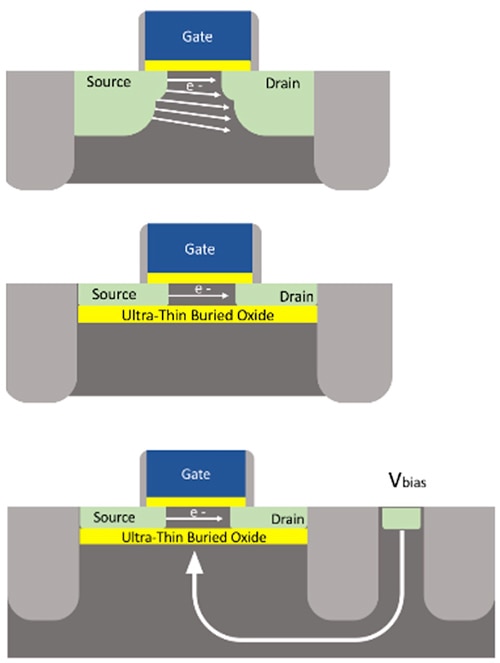

Op het meest fundamentele niveau combineert de i.MX 7ULP-familie fabricagemethoden die door middel van de geometrie van de transistor parasitaire elementen verlagen, waardoor de lekstroom en dus het dynamisch stroomverbruik wordt verminderd. In tegenstelling tot conventionele transistorstructuren (afbeelding 2, bovenaan), worden i.MX 7ULP-processors vervaardigd met een ultradunne onderliggende oxidelaag (Afbeelding 2, midden) die de elektronenstroom van de emitter naar de collector vermindert en daarmee de lekstroom verlaagt. Een verdere verbetering stelt ontwerpers in staat om forward body bias (FBB) of reverse body bias (RBB) toe te voegen (Afbeelding 2, onderaan).

Figuur 2: Een conventionele transistor kan aanzienlijke lekkage vertonen als elektronen van de emitter naar de collector stromen (boven), maar de NXP i.MX 7ULP-familie is gefabriceerd met een ultradunne onderliggende oxidelaag die de elektronenstroom belemmert (midden) en een structuur die de elektronenstroom verder versnelt of vertraagt d.m.v. forward body bias (FBB) of reverse body bias (RBB) (onder). (Bron: NXP)

Figuur 2: Een conventionele transistor kan aanzienlijke lekkage vertonen als elektronen van de emitter naar de collector stromen (boven), maar de NXP i.MX 7ULP-familie is gefabriceerd met een ultradunne onderliggende oxidelaag die de elektronenstroom belemmert (midden) en een structuur die de elektronenstroom verder versnelt of vertraagt d.m.v. forward body bias (FBB) of reverse body bias (RBB) (onder). (Bron: NXP)

Wanneer energie-efficiëntie een topprioriteit is, kunnen ontwikkelaars RBB gebruiken om de elektronenstroom te verlagen en dus de lekstroom en het totale stroomgebruik van het apparaat verder verminderen ten koste van de prestaties. Daarentegen kunnen ontwikkelaars met behulp van FBB de elektronenstroom verhogen en daarmee de prestaties verbeteren, wat dan weer leidt tot een hoger stroomverbruik als gevolg van een hogere lekstroom.

Op het chipontwerpniveau omvat de i.MX 7ULP-familie meerdere technieken, waaronder dynamische frequentieschaling (DFS) en dynamische spanningschaling (DVS), softwaregebaseerd clock gating (klokschakelen) en softwaregebaseerd power gating (schakelen van de voeding). Naast het verminderen van het stroomgebruik van verschillende randapparatuur kunnen ontwikkelaars deze functies ook gebruiken om blokken intern geheugen selectief af te sluiten of geheugen in verschillende energiebesparende modi te plaatsen.

Op architecturaal niveau is het mogelijk om stroomgebruik en prestaties verder af te stemmen door het gebruik van meerdere powerdomeinen, waaronder de eerder genoemde afzonderlijke powerdomeinen voor de Cortex-A7 en Cortex-M4-subsystemen.

Elk processorkern-powerdomein bevat FBB- en RBB-stuurprogramma's, speciale low-dropout (LDO)-regelaars en high level detector (HVD)- en low level detector (LVD)-monitors die zijn ontworpen om spanningsschommelingen boven of onder de aangegeven drempels te signaleren. Een afzonderlijke power-on-reset (PoR)-monitor volgt het spanningsniveau in het ‘always-on’-powerdomein.

Samen met de aparte powerdomeinen van de kern beheersen afzonderlijke powerdomeinen ook systeemfuncties zoals ‘always-on’-hardware, terwijl een batterijgevoed domein de voeding beheert voor kritieke functies, waaronder de realtime-klok en een veilige niet-vluchtige opslagmodule. Net als bij de powerdomeinen van de kernen ondersteunt elk van deze gespecialiseerde powerdomeinen een uitgebreide set gespecialiseerde energiebesparingsfuncties (waarvan er te veel zijn om afzonderlijk in één artikel te behandelen).

Om één voorbeeld te noemen: het powerdomein voor ‘always-on’-functionaliteit bevat een LLWU-module (low-leakage wake-up unit) waarmee ontwikkelaars meerdere externe pennen of interne modules kunnen gebruiken als wekbron voor de hieronder beschreven speciale low-leakage powermodi.

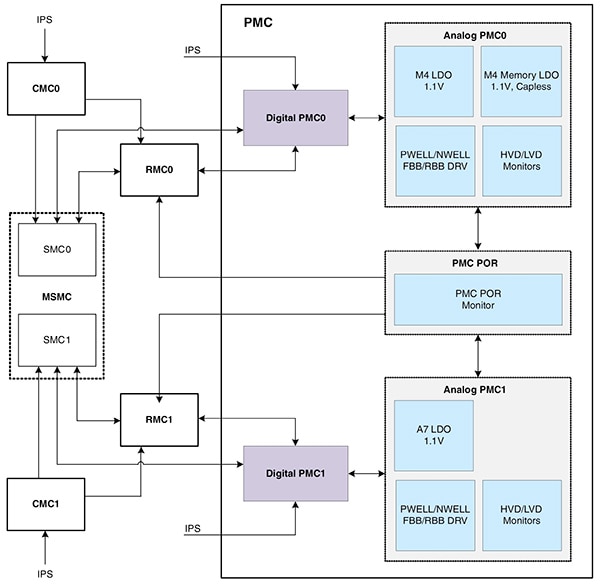

Deze architecturale functies zijn samengevoegd in de geïntegreerde powermanagementcontroller (PMC) van de processor, die deze afzonderlijke powerdomeinen en de powereilanden verwerkt (Afbeelding 3).

Afbeelding 3: De NXP i.MX 7ULP-familie integreert een geavanceerde besturingsfunctie waarmee ontwikkelaars powerdomeinen en powereilanden programmatisch kunnen configureren om stroomgebruik en prestaties af te stemmen op veranderende toepassingseisen. (Bron: NXP)

Afbeelding 3: De NXP i.MX 7ULP-familie integreert een geavanceerde besturingsfunctie waarmee ontwikkelaars powerdomeinen en powereilanden programmatisch kunnen configureren om stroomgebruik en prestaties af te stemmen op veranderende toepassingseisen. (Bron: NXP)

Op deze manier initiëren ontwikkelaars powermodusovergangen door opdrachten te verzenden via de normale intelligente perifere subsysteem (IPS)-bus naar een besturingscomplex bestaande uit drie nauw gekoppelde modules:

- Core Mode Controller (CMC), die meerdere kernfuncties ondersteunt

- Multicore System Mode Controller (MSMC), bestaande uit System Mode Controller 0 (SMC0) voor het Cortex-M4-powerdomein en SMC1 voor het Cortex-A7-powerdomein, die de volgorde tussen verschillende powermodi afhandelt, gebeurtenissen bewaakt die worden gebruikt om overgangen tussen powermodi te initiëren en de stroom-, klok- en geheugenfuncties regelt die zijn gekoppeld aan stroomgebruikoptimalisatie

- Reset Mode Controller (RMC), die chip reset-functies beheert

Afstemmen van stroomgebruik en prestaties

De i.MX 7ULP-familie biedt ontwikkelaars een vertrouwd programmeermodel voor alle powermanagementmogelijkheden. Net als bij andere geavanceerde processors levert de i.MX 7ULP verschillende low-power bedrijfstoestanden via een reeks programmeerbare low-power modi. De i.MX 7ULP-processorkernen ondersteunen verschillende softwaregestuurde low-power modi waarmee ontwikkelaars het stroomgebruik kunnen verlagen tot het laagst mogelijke niveau dat consistent is met de vereiste functionaliteit.

Met behulp van deze verschillende low-power modi kunnen ontwikkelaars één of beide kernen en bijbehorende subsystemen instellen op verschillende variaties van een normale RUN-modus, WAIT-modus en STOP-modus.

De normale RUN-modus en de high-speed HSRUN-modus zorgen voor krachtige prestaties ter ondersteuning van rekenintensieve onderdelen van een toepassing. In de HSRUN-modus werkt het kernsubsysteem op de hoogste frequentie. Als de toepassing lagere prestaties kan verdragen, kunnen ontwikkelaars de kern instellen in de Very Low Power Run (VLPR)-modus met een maximale frequentie van 48 megahertz (MHz) en een eveneens lager energieverbruik.

In de normale WAIT-modus is alle randapparatuur actief, maar wordt de kern geklokschakeld. Dit betekent dat deze in een statische toestand verkeert, maar klaar is om te worden gewekt na ontvangst van een wait-for-interrupt (WFI)-signaal. In deze modus kunnen ontwikkelaars autonome perifere bewerkingen buffers laten vullen of direct-memory-access (DMA)-transacties gebruiken om systeemgeheugen te vullen voordat een interrupt wordt afgegeven die de kern uit de WAIT-status haalt. In de Very Low Power Wait (VLPW)-modus werkt de randapparatuur gewoon op de gereduceerde frequentie, maar wordt de kern geklokschakeld.

Bij toepassingen zoals wearables of draagbare apparaten kan het systeem te maken krijgen met langere perioden van inactiviteit, wellicht periodiek onderbroken door een kortstondige uitbarsting van activiteit. In dat geval is energiebesparing van cruciaal belang voor de levensduur van de batterij. Wanneer de toepassing een langere wektijd voor de kern kan verdragen, is de mogelijkheid om het apparaat in een nog diepere slaaptoestand te plaatsen dan RUN, WAIT of een Very Low Power-variatie een bijzonder effectieve optie. Ontwikkelaars kunnen deze aanpak steunen door elk i.MX 7ULP-kernsubsysteem in een diepere slaapstand te plaatsen met verschillende wektijden:

- In de STOP-toestand kunnen sommige randapparaten asynchroon werken, maar blijft de kern in een statische toestand met een wektijd van 7 microseconden (μs) voor de Cortex-A7 of 7 μs voor de Cortex-M4.

- In de Very Low Power Stop (VLPS)-modus wordt de randapparatuur verder beperkt, maar blijft de kern in een statische toestand met een wektijd van 21,5 μs (Cortex-A7) of 9 μs (Cortex-M4).

Voor toepassingen met nog strengere eisen voor stroomgebruik kunnen ontwikkelaars elke kern in de volgende speciale low-leakage modi plaatsen die meer subsystemen uitschakelen:

- Low Leakage Stop (LLS), waarbij de klok de kern, bus en randapparatuur schakelt. Hierdoor blijft de kern in een WFI-toestand met een wektijd van 40 μs (Cortex-A7) of 58 μs (Cortex-M4).

- Very Low Leakage Stop (VLLS), waarbij de klok het gehele powerdomein van de kern schakelt. Dit leidt tot een langere wektijd zoals 60 μs voor de Cortex-A7 of 375 μs voor de Cortex-M4.

Voor nog grotere energiebesparingen kunnen ontwikkelaars in sommige powermodi, waaronder VLPS en LLS, RBB toepassen met een overeenkomstige afname van de prestaties en een incrementele toename van de wektijd van ongeveer 2 tot 4 μs.

Daarentegen kunnen ontwikkelaars voor rekenintensieve taken de kernen in een speciale HSRUN-modus plaatsen. In de HSRUN-modus schakelt de Cortex-A7-kern over van de normale werkfrequentie van 500 MHz naar een overdrive-modus die draait op 720 MHz.

Dankzij deze nauwkeurige besturing kunnen ontwikkelaars de i.MX 7ULP configureren om zelfs aan extreme stroomeisen te voldoen zonder essentiële functionaliteit in te leveren. Zo kan een toepassing bijvoorbeeld het laagst mogelijke stroomgebruik vereisen, maar tevens de realtime functionaliteit van de Cortex-M4-kern, evenals het gebruik van specifieke randapparatuur of geheugen van het Cortex-A7-subsysteem. In dat geval kan de ontwikkelaar het Cortex-A7-subsysteem in de STOP- of VLPS-status plaatsen en toegang hebben tot het geheugen of de randapparatuur vanaf de Cortex-M4, terwijl die kern real-time bewerkingen uitvoert. Ontwikkelaars kunnen nog meer energie besparen door de Cortex-M4-klok te gebruiken om de randapparatuur van de Cortex-A7 aan te sturen.

Eenvoudige systeemimplementatie

Voor het implementeren van een low-powersysteem met de i.MX 7ULP kunnen ontwikkelaars kiezen uit verschillende programmeerbare powermodi en configuraties afhankelijk van hun vermogens- en prestatievereisten. Wat de hardware betreft, is het systeemontwerp nog eenvoudiger.

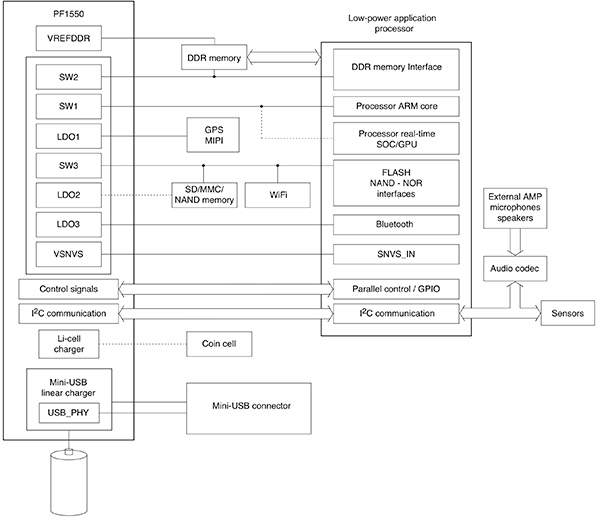

Voor de meest gangbare applicaties kunnen ontwikkelaars eenvoudigweg een i.MX 7ULP-processor combineren met de bijbehorende NXP MC32PF1550A3EPR2 powermanagement-IC (PMIC) en een ontwerp creëren dat gemengde taken kan verwerken zonder afbreuk te doen aan een beperkt energiebudget (Afbeelding 4).

Afbeelding 4: De NXP MC32PF1550A3EPR2 powermanagement-IC biedt de complete set voedingsbronnen die nodig zijn voor de NXP i.MX 7ULP-processor, waarbij het hardware-ontwerp wordt gereduceerd tot een eenvoudige combinatie van deze twee onderdelen en een aantal passieve componenten. (Bron: NXP)

Afbeelding 4: De NXP MC32PF1550A3EPR2 powermanagement-IC biedt de complete set voedingsbronnen die nodig zijn voor de NXP i.MX 7ULP-processor, waarbij het hardware-ontwerp wordt gereduceerd tot een eenvoudige combinatie van deze twee onderdelen en een aantal passieve componenten. (Bron: NXP)

De MC32PF1550A3EPR2 is specifiek ontworpen om te voldoen aan de spanningsbehoeften van NXP-processors, zoals de i.MX 7ULP-familie, en integreert drie geschakelde buck-regelaars (SW1, SW2, SW3), drie LDO-regelaars (LDO1, LDO2, LDO3), een geheugenreferentiespanningsbron, een complete eencellige lithiumbatterijlader en eenmalig programmeerbaar (OTP) geheugen voor configuratie.

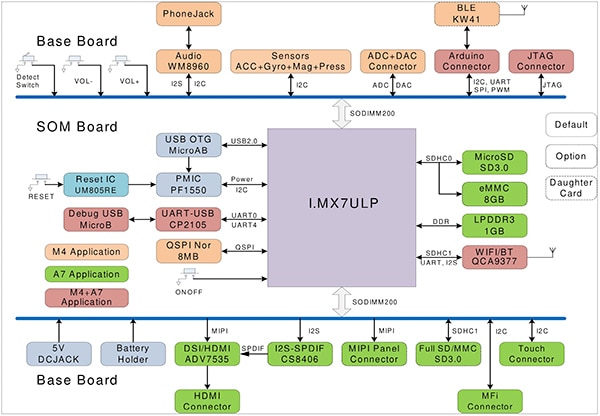

De MCIMX7ULP-EVK-evaluatiekit van NXP levert de eenvoudige hardware-interface die nodig is om het MC32PF1550A3EPR2 PMIC en i.MX 7ULP-onderdelen te combineren. De kit bestaat uit een system-on-module (SOM)-kaart die de i.MX 7ULP-processor en de MC32PF1550A3EPR2 PMIC bevat, een basisprint met meerdere sensoren, draadloze mogelijkheden, een audiocodec, een SD-connector en diverse andere connectoren, waaronder JTAG en Arduino (Afbeelding 5).

Afbeelding 5: De evaluatiekit MCIMX7ULP-EVK bestaat uit een combinatie van een system-on-module (SOM)-kaart, die een i.MX 7ULP-processor en MC32PF1550A3EPR2 PMIC bevat, en basisprint met sensoren, connectoren en andere componenten die nodig zijn voor softwareontwikkeling met i.MX 7ULP-processors. (Bron: NXP)

Afbeelding 5: De evaluatiekit MCIMX7ULP-EVK bestaat uit een combinatie van een system-on-module (SOM)-kaart, die een i.MX 7ULP-processor en MC32PF1550A3EPR2 PMIC bevat, en basisprint met sensoren, connectoren en andere componenten die nodig zijn voor softwareontwikkeling met i.MX 7ULP-processors. (Bron: NXP)

Hoewel de evaluatiekit ‘out-of-the-box’ functionaliteit bevat, biedt NXP ook downloadbare ontwerpbestanden, tools en kaartondersteuningspakketten voor aangepaste software met FreeRTOS voor realtime code, evenals Linux of Android voor applicatiecode.

Conclusie

De vraag naar meer geavanceerde functionaliteit en een langere levensduur van de batterij in mobiele producten heeft ontwikkelaars van oudsher gedwongen een compromis te sluiten tussen vermogen en prestaties. Ook wordt een verder compromis tussen realtime-capaciteiten en prestaties op applicatieniveau gestuurd door groeiende verwachtingen voor tijdige gegevens van meer sensoren in IoT-apparaten, wearables en andere draagbare producten.

Zoals aangetoond, kunnen ontwikkelaars zich echter wenden tot HMP-architecturen, zoals die gebruikt in de i.MX 7ULP-processorfamilie van NXP, om te voldoen aan strenge ultra-low-power vereisten zonder capaciteiten in te leveren.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.