Gebruik flashloze microcontrollers voor lagere systeemkosten en verbeterde prestaties

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2019-08-22

Naarmate netwerken voor Internet of Things, oftewel IoT-netwerken, steeds gecompliceerdere taken moeten uitvoeren, nemen de geheugenvereisten voor IoT-eindpunten ook toe, vooral voor eindpunten die edge computing op hogere niveaus uitvoeren. On-chip microcontroller flashgeheugen is echter beperkt tot circa 1 megabit (Mbit) en veel high-end IoT-eindpunten gebruiken vele malen meer geheugen dan dat.

De conventionele oplossing was om het programmageheugen van de microcontroller uit te breiden met een externe flashchip. Wanneer we het echter over geheugenvereisten van 8 Mbit of meer hebben, is het grootste deel van het programmageheugen off-chip.

Als gevolg hiervan kunnen ontwerpers in veel gevallen beter van on-chip flash afzien en in plaats daarvan een flashloze — ook wel ROMloze genoemd — microcontroller gebruiken, gekoppeld aan een externe, snelle octale SPI eXecute-in-place (XiP) flashchip. Hierdoor worden de kosten van de microcontroller aanzienlijk minder en is het ontwerp dankzij grotere schaalbaarheid meer toekomstbestendig. Alle problemen met geheugentoegangstijden worden tenietgedaan door de opkomst van zeer snelle octale geheugeninterfaces.

In dit artikel worden ROMloze microcontrollers en externe geheugens besproken en de evolutie naar een haalbare optie voor IoT-eindpunten en ingebedde systemen die grote hoeveelheden programmageheugen vereisen. Vervolgens wordt getoond hoe het concept kan worden toegepast met ROMloze microcontrollers van NXP Semiconductors en een octale SPI XiP flashchip vanAdesto Technologies.

Geheugenuitbreiding voor IoT-eindpunten

De meeste IoT-eindpunten met lage tot gemiddelde capaciteit maken gebruik van een microcontroller om het eindpunt te beheren en slaan de firmware op in on-chip flashgeheugen. Maar firmware neemt toe door extra applicatiecode, draadloze IP-communicatiestacks en verbeterde beveiligingscode toe te voegen. Deze code-uitbreiding kan plaatsvinden tijdens de ontwikkeling en als gevolg van veldupdates.

Bovendien worden sommige van deze IoT-eindpunten nu gebruikt om meer rekenfuncties uit te voeren. In plaats van onbewerkte of gedeeltelijk verwerkte sensorgegevens via het netwerk voor verwerking naar een centrale computer te versturen, voeren IoT-eindpunten complexere taken zelf uit, zoals sensorfusie-algoritmen, gegevensinterpolatie, patroon- of beeldherkenning en steeds complexere AI-algoritmes (kunstmatige intelligentie).

Als gevolg voert de centrale computer alleen het resultaat van de lokale verwerking van het IoT-knooppunt ontvangt, in plaats van elke byte onbewerkte sensorgegevens, wat kan leiden tot minder verkeer op het draadloze netwerk. Omdat de RF-zender wellicht de grootste stroomafnemer in een IoT-eindpunt is, leidt edge computing vaak tot een langere batterijduur voor eindpunten die op batterijen werken.

Systemen die in het veld moeten worden bijgewerkt, worden geconfronteerd met extra geheugenproblemen. Conventionele systemen hebben minstens tweemaal de geschatte hoeveelheid programmageheugen nodig om dergelijke updates te kunnen verwerken. Dit is om zowel het bestaande programmageheugen als de grootte van eventuele OTA-updates (over-the-air) te kunnen verwerken. Sommige systemen kunnen wel driemaal het geschatte programmageheugen nodig hebben, waarbij het extra geheugen wordt toegewezen aan een alleen-lezen-kopie van de fabrieksfirmware. Bij bepaalde soorten systeemstoringen, zoals in geval van hacken of een beschadigde firmware-installatiekopie, kan het systeem zo de oorspronkelijke fabrieksfirmware laden om het systeem te herstellen.

Voor sommige toepassingen kan deze geheugenuitbreiding snel de ingebedde flashlimiet van 1 Mbit overschrijden, waardoor externe geheugenuitbreiding nodig is. Traditioneel werd dit probleem opgelost door een externe parallelle flashgeheugenchip toe te voegen. Dit heeft echter als nadeel dat hiervoor ongeveer 36 externe pennen op de microcontroller worden gebruikt — pennen die anders zouden kunnen worden gebruikt voor applicatie-I/O. Tevens neemt dit onnodige printplaatruimte in en is er een grotere kans op elektromagnetische interferentie (EMI) van de kaart.

Uitbreiding SPI-programmageheugen

Naast het gebruik van een parallelle bus kan het programmageheugen ook worden uitgebreid met behulp van de Serial Peripheral Interface (SPI). Terwijl de conventionele SPI slechts één datalijn gebruikt voor half-duplex single-bit transmissies, is deze in de loop der jaren gegroeid en ondersteunt nu dubbele en quad datalijnen, wat resulteert in een overeenkomstige toename in gegevensdoorvoer. Deze doorvoer is toegenomen tot een punt waarop het praktisch is om over te stappen op een externe SPI flashchip met grote capaciteit.

Een conventionele dual of quad SPI gebruikt voor programmageheugentoepassingen een shadow-flashconfiguratie waarbij het externe flashgegevensgeheugen wordt gekopieerd naar een ingebed statisch random access memory (SRAM) dat wordt toegewezen aan programmageheugenruimte. Hoewel het voordeel hiervan is dat het programmageheugen eenvoudig kan worden uitgebreid terwijl de uitvoeringssnelheid wordt verbeterd door de snelle SRAM te gebruiken, heeft het ook belangrijke nadelen. Omdat de hoeveelheid interne SRAM beperkt is, wordt het geheugen in een wisselbare modus gebruikt terwijl flashgeheugen zo nodig wordt omgewisseld in interne SRAM. Dit probleem kan worden opgelost door meer SRAM op de chip te plaatsen, maar omdat SRAM één van de duurste blokken op een halfgeleider is, maakt dit de microcontroller aanzienlijk duurder.

Een recentere evolutie van SPI is XiP. Met SPI XiP kan de CPU van de microcontroller de firmware-code rechtstreeks vanaf het externe SPI flashgeheugen uitvoeren. De uitvoeringssnelheid van het programma kan aanzienlijk worden verbeterd door een cache toe te voegen aan de SPI XiP-interface.

De populariteit van SPI XiP heeft geleid tot een recente uitbreiding van de interface met acht datalijnen. Deze octale SPI XiP-interface heeft de doorvoer zodanig verhoogd dat het veel sneller is dan uitvoeren vanaf het on-chip flashgeheugen — sneller dan 100 Mbit/s.

SPI-geheugenrevolutie

Dit heeft geleid tot een merkwaardige evolutie naar iets wat 30 jaar geleden al werd gebruikt. Neem nu een systeem met 1 Mbit on-chip flashgeheugen en 32 Mbit extern programmageheugen dat flash-toegankelijk is via een octale SPI XiP-interface. Het on-chip programmageheugen is zo klein dat men zich kan afvragen of die on-chip microcontroller-flash wellicht kan worden geëlimineerd terwijl het systeem toch kosteneffectief blijft.

Er is lang van uitgegaan dat een mid-range-systeem met een flash-microcontroller steevast goedkoper is dan een systeem met een flashloze microcontroller en een externe flashchip. Dat is pas recentelijk veranderd.

Als het on-chip flashgeheugen wordt verwijderd, verlaagt dit uiteraard de kosten van de microcontroller. Maar nader onderzoek toont aan dat als het flashgeheugen niet langer nodig is, de procestechnologiefuncties die alleen voor flash worden gebruikt ook kunnen worden geëlimineerd. Dit verlaagt de kosten van het productieproces, waardoor de kosten van de microcontroller aanzienlijk worden verlaagd. Een gevolg hiervan is een heropleving van wat zo'n 30 jaar geleden de ‘ROMloze’ microcontroller werd genoemd. Tegenwoordig noemen we dat ‘flashloos’.

De (her)introductie van flashloze microcontrollers

De flashloze MIMXRT1052DVL6B (RT1052) van NXP Semiconductors is een krachtige microcontroller die gebruik maakt van de flashgeheugensnelheid. De RT1052 is lid van NXP’s i.MX RT1050-processorfamilie en gebaseerd op een 600 megahertz (MHz) Arm® Cortex®-M7 met een instructiecache van 32 kbyte en een gegevenscache van 32 kbyte. De kloksnelheid van 600 MHz wordt bereikt door de flash te verwijderen en gebruik te maken van snelle CMOS-procestechnologie die niet wordt beperkt door intern flashgeheugen. De RT1052 heeft een grote hoeveelheid SRAM — 512 kilobyte (kbyte) — die kan worden gepartitioneerd voor programma- of gegevensgeheugengebruik.

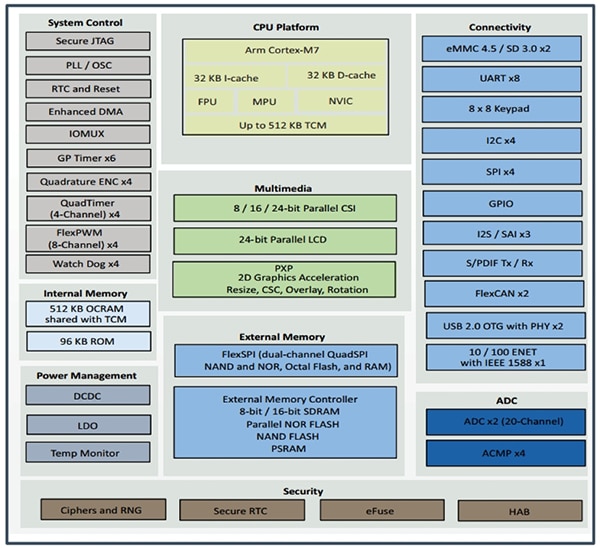

De microcontroller heeft diverse high-end randapparatuur, waaronder een LCD-interface, een digitale camera-sensor-interface (CSI) en Pixel Processing Pipeline (PXP) voor hoogwaardige cameraondersteuning, een SPDIF-interface voor digitale audio, twee USB OTG-interfaces, twee eMMC/SD-flashkaartinterfaces, twee 20-kanaals analoog-digitaalomzetters (ADC's) en een coderingsmodule. Een complete lijst van randapparatuur is te zien in het blokdiagram (Afbeelding 1).

Afbeelding 1: De NXP RT1052 heeft tal van high-end randapparatuur, waaronder een SPI XiP seriële interface en ondersteuning voor gegevenscodering. (Bron afbeelding: NXP)

Afbeelding 1: De NXP RT1052 heeft tal van high-end randapparatuur, waaronder een SPI XiP seriële interface en ondersteuning voor gegevenscodering. (Bron afbeelding: NXP)

Een andere optie is de NXP MIMXRT1051DVL6B (RT1051). Deze heeft exact dezelfde functies als de RT1052, maar zonder de LCD-interface, CSI en PXP.

De RT1052 heeft een FlexSPI-interface die code kan uitvoeren met behulp van dual, quad of octale SPI XiP-flashinterfaces. Voor extra firmwarebeveiliging ondersteunt de microcontroller gecodeerd programmageheugen via SPI XiP, een goed voorbeeld hiervan is de ATXP032-CCUE-T van Adesto Technologies.

Moderne XiP-flashtoepassing

De ATXP032-CCUE-T van Adesto is een 32 Mbit octale flashchip die gegevensoverdracht ondersteunt tot 266 megabyte (Mbyte) per seconde in octale dual transfer rate (DTR) modus — veel sneller dan on-chip microcontroller flashgeheugen. Dit vereist een enkele voeding van 1,8 volt en heeft een typische octale standby-stroom van 35 microampère (µA). De chip ondersteunt een maximale SPI-kloksnelheid van 133 MHz.

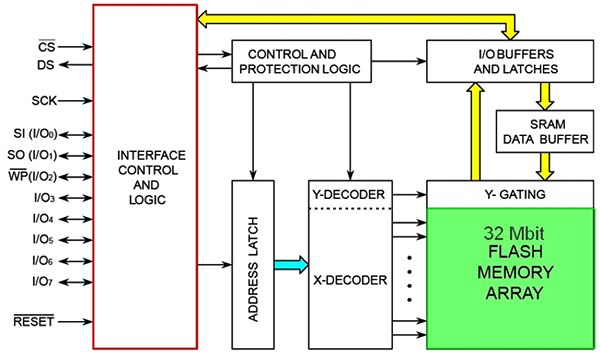

Afbeelding 2: Het Adesto ATXP032-CCUE-T flashgeheugen gebruikt een octale SPI, I/O0 tot I/O7, voor communicatie met een microcontroller. Een SRAM-schrijfdatabuffer verbetert de prestaties van schrijf-naar-flash-bewerkingen. (Bron afbeelding: Adesto Technologies)

Afbeelding 2: Het Adesto ATXP032-CCUE-T flashgeheugen gebruikt een octale SPI, I/O0 tot I/O7, voor communicatie met een microcontroller. Een SRAM-schrijfdatabuffer verbetert de prestaties van schrijf-naar-flash-bewerkingen. (Bron afbeelding: Adesto Technologies)

Tijdens een actieve flash-read trekt de ATXP32 een stroom van 142 µA/MHz plus 1 milliampère (mA) overhead (typisch). Met een maximale SPI-kloksnelheid van 133 MHz in octale modus trekt hij slechts 19,9 mA.

De ATXP032-CCUE-T ondersteunt ook standaard SPI-modus 0 en 3, evenals de quad SPI-modus. Een beveiligingsregister van 256 byte heeft een in de fabriek geprogrammeerde unieke id van 128 byte, evenals 128 byte eenmalig OTP-geheugen dat kan worden gebruikt om apparaatinformatie op te slaan, zoals een Ethernet MAC-adres (Media Access Control) of een beveiligingssleutel.

De geheugenindeling van de ATXP032-CCUE-T is opmerkelijk. Het is verdeeld in vier banken van elk 8 Mbit. De interne logica is zo geconfigureerd dat een host-microcontroller vanuit de ene bank code kan uitvoeren tijdens het programmeren of wissen van een andere. De bewerking is transparant voor de host-microcontroller en vereist geen speciale configuratie-instellingen.

De ATXP032-CCUE-T heeft ook drie status- en besturingsregisters voor het configureren van de bedrijfsparameters, zoals de energiebesparende modus, het in- of uitschakelen van de DTR-modus en het instellen van standaard, quad of octale SPI-modi (de fabrieksinstelling is standaard SPI). De statusregisters kunnen de status van een programma- of een wisbewerking aangeven, de energiebesparende status en of (een gedeelte van) het geheugen tegen schrijven is beveiligd.

Combinatie van flashloze microcontrollers en externe XiP

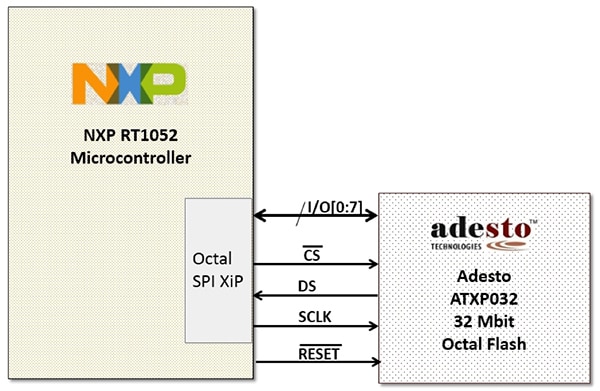

De RT1052 en de ATXP032-CCUE-T kunnen eenvoudig worden gecombineerd (Afbeelding 3). Bij het opstarten begint de RT1052 met het uitvoeren van code uit de 96 kbyte aan on-chip opstart-ROM. Het opstart-ROM leest de status van 14 opstartconfiguratiepennen die bepalen welke van de vele RT1052 externe geheugeninterfaces voor programmageheugen worden gebruikt. Mogelijke opties zijn een externe eMMC-kaart, een micro SD-kaart, een conventionele externe parallelle interface of de SPI XiP (in dit geval de ATXP032-CCUE-T van Adesto).

Afbeelding 3: De NXP RT1052 flashloze microcontroller heeft een octale SPI XiP-interface die gemakkelijk kan worden gekoppeld aan de Adesto ATXP032-CCUE-T. De octale SPI XiP-interfacebewerking is transparant voor de Arm-kern. (Bron afbeelding: DigiKey)

Afbeelding 3: De NXP RT1052 flashloze microcontroller heeft een octale SPI XiP-interface die gemakkelijk kan worden gekoppeld aan de Adesto ATXP032-CCUE-T. De octale SPI XiP-interfacebewerking is transparant voor de Arm-kern. (Bron afbeelding: DigiKey)

De opstartopties van de RT1052 omvatten ook het downloaden van code van de USB OTG of een UART die moet worden uitgevoerd vanaf SRAM. De opstartmodusopties kunnen ook tijdens de productie worden ingesteld door interne fuses in de RT1052 te verbreken in plaats van de configuratiepennen van de opstartmodus te gebruiken. Als de octale SPI XiP-interface eenmaal het programmageheugen door de opstart-ROM van de RT1052 kan uitvoeren, wordt het programma onmiddellijk uitgevoerd. De Arm-kern voert vervolgens firmware van de Adesto ATXP032-CCUE-T uit op dezelfde manier als van een externe parallelle flashchip of interne flash.

Vanwege de snelle gegevensoverdracht moet de octale seriële flash zo dicht mogelijk bij de octale SPI XiP-poort van de microcontroller op de printplaat worden geplaatst. Om interferentie te verminderen, mogen de printsporen niet langer zijn dan 120 millimeter (mm). De afstand tussen het kloksignaal en andere signalen moet minstens driemaal de breedte van de printsporen zijn, om interferentie te voorkomen. De I/O [0:7] bidirectionele gegevenssignalen moeten allemaal binnen 10 mm van elkaar liggen om verschillen in aankomsttijd te voorkomen.

Conclusie

IoT-eindpunten vereisen meer en meer geheugen vanwege trends in edge computing en de behoefte aan OTA-updates en bijbehorende geheugenschaalbaarheid. Vroeg of laat kunnen ontwerpers van deze eindpuntapparaten het gebruik van een flashloze microcontrollers overwegen.

Zoals is aangetoond, bieden ontwikkelingen in flashloze microcontrollers, snelle interfaces en octale SPI XiP-flashchips ontwikkelaars de mogelijkheid om hoogwaardige, kosteneffectieve IoT-eindpunten of ingebedde systemen te bouwen in plaats van traditionele op flash gebaseerde microcontrollers te gebruiken.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.