Gebruik het snelle FPGA-pad om krachtige, energiezuinige edge AI-applicaties te bouwen

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2021-01-12

Ontwerpers die op zoek zijn naar kunstmatige intelligentie (AI)-algoritmen op inferentieprocessoren aan de rand, staan onder constante druk om het stroomverbruik en de ontwikkelingstijd te verlagen, zelfs als de verwerkingseisen toenemen. Veldgeprogrammeerde gate arrays (FPGA's) bieden een bijzonder effectieve combinatie van snelheid en vermogensefficiëntie voor de implementatie van de NN-conferentiemotoren (NN) die nodig zijn voor edge AI. Voor ontwikkelaars die niet bekend zijn met FPGA's kunnen de conventionele FPGA-ontwikkelingsmethoden echter complex lijken, waardoor ontwikkelaars zich vaak tot minder optimale oplossingen wenden.

Dit artikel beschrijft een eenvoudigere aanpak van Microchip Technologie waarmee ontwikkelaars de traditionele FPGA-ontwikkeling kunnen omzeilen om getrainde NN's te maken met behulp van FPGA's en een softwareontwikkelingskit (SDK), of een FPGA-gebaseerde videokit kunnen gebruiken om direct over te gaan op slimme ingebedde vision-toepassingontwikkeling.

Waarom AI aan de egde gebruiken?

Edge computing brengt een aantal voordelen met zich mee voor Internet of Things (IoT)-toepassingen in uiteenlopende segmenten zoals industriële automatisering, beveiligingssystemen, slimme huizen en meer. In een industriële IoT-toepassing (IIoT) die zich richt op de fabrieksvloer, kan edge computing de reactietijd in procesregelcircuits drastisch verbeteren door het elimineren van roundtrip-vertragingen naar cloudgebaseerde toepassingen. Op dezelfde manier kan een rand-gebaseerd beveiligingssysteem of slim huisdeurslot blijven functioneren, zelfs wanneer de verbinding met de cloud per ongeluk of opzettelijk wordt verbroken. In veel gevallen kan het gebruik van edge computing in een van deze toepassingen helpen de totale operationele kosten te verlagen door de afhankelijkheid van het product van cloudbronnen te verminderen. In plaats van geconfronteerd te worden met een onverwachte behoefte aan extra dure cloudmiddelen als de vraag naar hun producten toeneemt, kunnen ontwikkelaars vertrouwen op de lokale verwerkingsmogelijkheden die in hun producten zijn ingebouwd om de bedrijfskosten stabieler te houden.

De snelle acceptatie en de toegenomen vraag naar machine learning (ML) inferentiemodellen versterken het belang van edge computing drastisch. Voor ontwikkelaars helpt de lokale verwerking van inferentiemodellen bij het verminderen van de responslatentie en de kosten van cloud-resources die nodig zijn voor cloud-gebaseerde inferentie. Voor gebruikers voegt het gebruik van lokale inferentiemodellen het vertrouwen toe dat hun producten zullen blijven functioneren ondanks incidenteel verlies van internetconnectiviteit of veranderingen in het cloud-gebaseerde aanbod van de productverkoper. Bovendien kan de bezorgdheid over de veiligheid en de privacy de noodzaak van lokale verwerking en gevolgtrekking verder stimuleren om de hoeveelheid gevoelige informatie die via het openbare internet naar de cloud wordt overgebracht, te beperken.

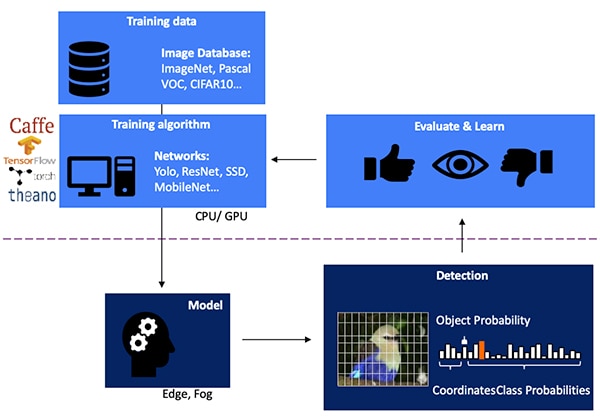

Het ontwikkelen van een NN-conferentiemodel voor vision-based objectdetectie is een meerstappenproces dat begint met modeltraining, meestal uitgevoerd op een ML-raamwerk zoals TensorFlow, waarbij gebruik wordt gemaakt van publiek beschikbare gelabelde afbeeldingen of aangepaste gelabelde afbeeldingen. Vanwege de verwerkingseisen wordt de modeltraining meestal uitgevoerd met grafische verwerkingseenheden (GPU's) in de cloud of een ander high-performance computerplatform. Na afloop van de training wordt het model omgezet naar een inferentiemodel dat in staat is om te draaien op edge- of foggercomputers en de inclusieresultaten te leveren als een set van objectklassekansen (Afbeelding 1).

Afbeelding 1: Het implementeren van een inferentiemodel voor edge AI ligt aan het einde van een meerstappenproces dat training en optimalisatie van NN's op basis van beschikbare of aangepaste trainingsgegevens vereist. (Bron afbeelding: Microchip Technology)

Afbeelding 1: Het implementeren van een inferentiemodel voor edge AI ligt aan het einde van een meerstappenproces dat training en optimalisatie van NN's op basis van beschikbare of aangepaste trainingsgegevens vereist. (Bron afbeelding: Microchip Technology)

Waarom inferentiemodellen een rekenkundige uitdaging zijn

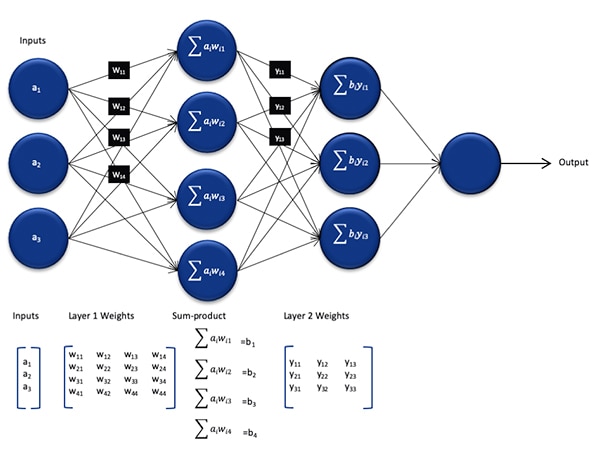

Hoewel de omvang en de complexiteit in vergelijking met het tijdens het opleidingsproces gebruikte model zijn afgenomen, vormt een NN-conferentiemodel nog steeds een rekenuitdaging voor processoren voor algemeen gebruik vanwege het grote aantal berekeningen dat het vereist. In zijn generieke vorm bestaat een diep NN-model uit meerdere lagen van sets neuronen. Binnen elke laag in een volledig aangesloten netwerk moet elke neuron nij de som van de producten van elke input met een bijbehorend gewicht wij berekenen (Afbeelding 2).

Afbeelding 2: Het aantal berekeningen dat nodig is voor inferentie met een NN, kan een aanzienlijke rekenkracht met zich meebrengen.brengen. (Bron afbeelding: Microchip Technology)

Afbeelding 2: Het aantal berekeningen dat nodig is voor inferentie met een NN, kan een aanzienlijke rekenkracht met zich meebrengen.brengen. (Bron afbeelding: Microchip Technology)

Niet weergegeven in Afbeelding 2 is de extra rekenkundige eis die wordt gesteld door de activeringsfunctie die de output van elk neuron wijzigt door het in kaart brengen van negatieve waarden naar nul, het in kaart brengen van waarden groter dan 1 tot 1, en soortgelijke functies. De output van de activeringsfunctie voor elke neuron nij dient als input voor de volgende laag i+1, en gaat op deze manier verder voor elke laag. Ten slotte produceert de outputlaag van het NN-model een outputvector die de waarschijnlijkheid weergeeft dat de oorspronkelijke inputvector (of -matrix) overeenkomt met een van de klassen (of labels) die tijdens het begeleide leerproces worden gebruikt.

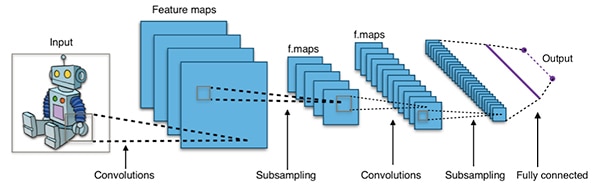

Effectieve NN-modellen worden gebouwd met architecturen die veel groter en complexer zijn dan de representatieve generieke NN-architectuur die hierboven is afgebeeld. Bijvoorbeeld, een typische convolutionele NN (CNN) die wordt gebruikt voor de detectie van beeldobjecten past deze principes toe op een stukgewijze manier, waarbij wordt gescand over de breedte, hoogte en kleurdiepte van een invoerafbeelding om een reeks functiekaarten te produceren die uiteindelijk de outputvoorspellingsvector opleveren (Afbeelding 3).

Afbeelding 3: CNN's die voor de detectie van beeldobjecten worden gebruikt, hebben betrekking op grote aantallen neuronen in vele lagen, waardoor er meer vraag is naar het berekeningsplatform. (Bron afbeelding: Aphex34 CC BY-SA 4.0)

Afbeelding 3: CNN's die voor de detectie van beeldobjecten worden gebruikt, hebben betrekking op grote aantallen neuronen in vele lagen, waardoor er meer vraag is naar het berekeningsplatform. (Bron afbeelding: Aphex34 CC BY-SA 4.0)

FPGA's gebruiken om NN-berekeningen te versnellen

Hoewel er een aantal opties blijven bestaan voor het uitvoeren van inferentiemodellen aan de rand, zijn er maar weinig alternatieven die een optimale mix van flexibiliteit, prestaties en vermogensefficiëntie bieden die nodig is voor praktische hogesnelheidsinferentie aan de egde. Van de gemakkelijk beschikbare alternatieven voor edge AI zijn FPGA's bijzonder effectief omdat ze een krachtige, op hardware gebaseerde uitvoering van rekenintensieve bewerkingen kunnen bieden, terwijl ze relatief weinig stroom verbruiken.

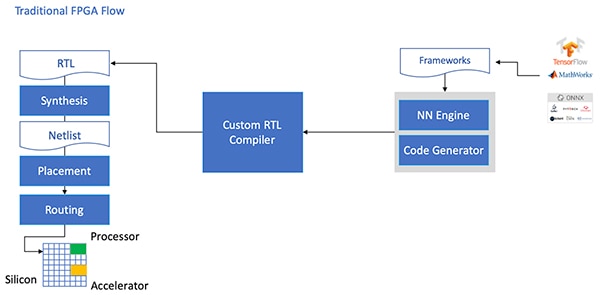

Ondanks hun voordelen worden FPGA's soms omzeild door een traditionele ontwikkelingsstroom die ontmoedigend kan zijn voor ontwikkelaars zonder uitgebreide FPGA-ervaring. Om een effectieve FPGA-implementatie van een NN-model, gegenereerd door een NN-raamwerk, te creëren, zou de ontwikkelaar de nuances moeten begrijpen van het omzetten van het model in registertransfertaal (RTL), het synthetiseren van het ontwerp, en het werken door de uiteindelijke plaats en route fysieke ontwerpfase om een geoptimaliseerde implementatie te produceren (Afbeelding 4).

Afbeelding 4: Om een NN-model op een FPGA te implementeren, moesten ontwikkelaars tot nu toe begrijpen hoe ze hun modellen naar RTL moesten converteren en via de traditionele FPGA-flow moesten werken. (Bron afbeelding: Microchip Technology)

Afbeelding 4: Om een NN-model op een FPGA te implementeren, moesten ontwikkelaars tot nu toe begrijpen hoe ze hun modellen naar RTL moesten converteren en via de traditionele FPGA-flow moesten werken. (Bron afbeelding: Microchip Technology)

Met zijn PolarFire FPGA's, gespecialiseerde software en bijbehorende intellectuele eigendom (IP), biedt Microchip Technology een oplossing die krachtige, laagvermogenige gevolgtrekkingen aan de rand breed beschikbaar maakt voor ontwikkelaars zonder FPGA-ervaring.

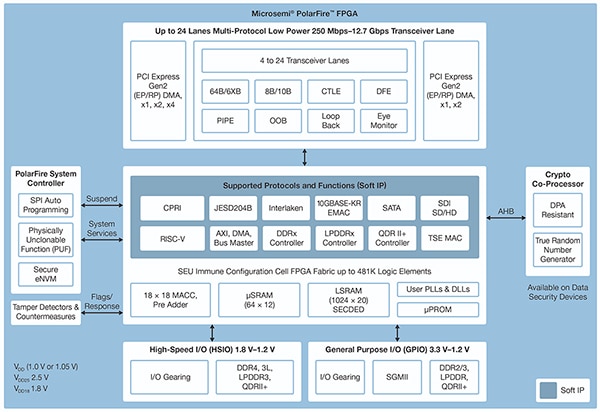

De PolarFire FPGA's zijn vervaardigd in een geavanceerde niet-vluchtige procestechnologie en zijn ontworpen om de flexibiliteit en prestaties te maximaliseren en tegelijkertijd het stroomverbruik te minimaliseren. Samen met een uitgebreide reeks snelle interfaces voor communicatie en input/output (I/O) zijn ze voorzien van een diep FPGA-weefsel dat in staat is om geavanceerde functionaliteit te ondersteunen met behulp van zachte IP-kernen, waaronder RISC-V-processors, geavanceerde geheugencontrollers en andere standaard interfacesubsystemen (Afbeelding 5).

Afbeelding 5: De PolarFire-architectuur van de Microchip Technology biedt een diepe stof die is ontworpen ter ondersteuning van krachtige ontwerpvereisten, waaronder de implementatie van rekenintensieve inferentiemodellen. (Bron afbeelding: Microchip Technology)

Afbeelding 5: De PolarFire-architectuur van de Microchip Technology biedt een diepe stof die is ontworpen ter ondersteuning van krachtige ontwerpvereisten, waaronder de implementatie van rekenintensieve inferentiemodellen. (Bron afbeelding: Microchip Technology)

Het PolarFire FPGA-weefsel biedt een uitgebreide set logische elementen en gespecialiseerde blokken, die in verschillende capaciteiten worden ondersteund door verschillende leden van de PolarFire FPGA-familie, waaronder de MPF100T, MPF200T, MPF300T en MPF500T-serie (Tabel 1).

|

Tabel 1: In de PolarFire-reeks zijn verschillende FPGA-weefseleigenschappen en -capaciteiten beschikbaar. (Bron tabel: DigiKey, gebaseerd op Microchip Technology PolarFire datasheet)

De PolarFire-architectuur heeft onder meer een speciaal rekenblok dat een 18-bits × 18-bits signed multiply-accumulate-functie (MAC) met een pre-adder biedt, wat bijzonder interessant is voor de gevolgversnelling. Een ingebouwde dotproductmodus maakt gebruik van een enkel wiskundig blok om twee 8-bits vermenigvuldigingsbewerkingen uit te voeren, wat een mechanisme biedt om de capaciteit te verhogen door gebruik te maken van de verwaarloosbare impact van de modelkwantisering op de nauwkeurigheid.

Naast het versnellen van de wiskundige bewerkingen, helpt de PolarFire-architectuur het soort geheugencongestie te verlichten dat optreedt bij het implementeren van inferentiemodellen op architecturen voor algemene doeleinden, zoals kleine gedistribueerde geheugens voor het opslaan van tussentijdse resultaten die tijdens de uitvoering van het NN-algoritme worden gecreëerd. Ook kunnen de gewichten en biaswaarden van een NN-model worden opgeslagen in een 16-diep bij 18-bits alleen-lezen geheugen (ROM) dat is opgebouwd uit logische elementen die zich in de buurt van het rekenblok bevinden.

In combinatie met andere PolarFire FPGA-stoffuncties vormen de wiskundeblokken de basis voor het hogere niveau CoreVectorBlox IP van Microchip Technology. Dit dient als een flexibele NN-motor die verschillende soorten NN's kan uitvoeren. De CoreVectorBlox IP bevat samen met een set controleregisters drie grote functionele blokken:

- Microcontroller: Een eenvoudige RISC-V-softprocessor die het binaire grote object (BLOB) van de Microchip-firmware en het specifieke NN BLOB-bestand van de gebruiker uit de externe opslag leest. Het controleert de algemene CoreVectorBlox-bewerkingen door instructies van de firmware BLOB uit te voeren.

- Matrix processor (MXP): Een zachte processor die bestaat uit acht 32-bits rekenkundige logische eenheden (ALU's) en is ontworpen om parallelle bewerkingen uit te voeren op gegevensvectoren met behulp van elementaire tensorbewerkingen, waaronder add, sub, xor, shift, mul, dotprod en andere, met een gemengde 8-bits, 16-bits en 32-bits precisie, indien nodig.

- CNN-versneller: Versnelt MXP-bewerkingen met behulp van een tweedimensionale reeks MAC-functies die met behulp van wiskundige blokken zijn geïmplementeerd en met 8-bits precisie werken.

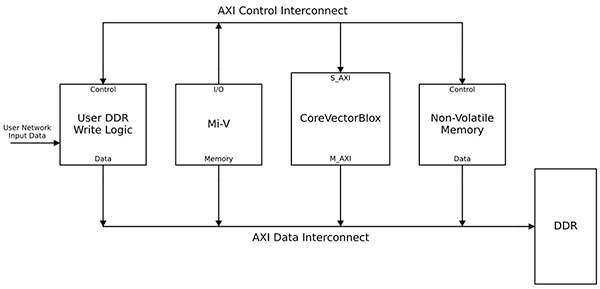

Een compleet NN-verwerkingssysteem zou een CoreVectorBlox IP-blok, geheugen, geheugencontroller en een hostprocessor combineren, zoals de Microsoft RISC-V (Mi-V)-softwareprocessorkern (Afbeelding 6).

Afbeelding 6: Het CoreVectorBlox IP blok werkt met een host processor zoals de Mi-V RISC-V microcontroller van de Microchip om een NN-conferentiemodel te implementeren. (Bron afbeelding: Microchip Technology)

Afbeelding 6: Het CoreVectorBlox IP blok werkt met een host processor zoals de Mi-V RISC-V microcontroller van de Microchip om een NN-conferentiemodel te implementeren. (Bron afbeelding: Microchip Technology)

In een videosysteemimplementatie zou de hostprocessor de firmware en netwerk-BLOB's uit het flashgeheugen van het systeem laden en deze kopiëren naar het dubbel data rate (DDR) random access memory (RAM) voor gebruik door het CoreVectorBlox-blok. Als de videoframes aankomen, schrijft de hostprocessor ze in DDR-RAM en signaleert het CoreVectorBlox-blok om te beginnen met de verwerking van de afbeelding. Nadat het het in het netwerk BLOB gedefinieerde inferentiemodel is uitgevoerd, schrijft het CoreVectorBlox-blok de resultaten, inclusief de beeldclassificatie, terug in DDR RAM voor gebruik door de doeltoepassing.

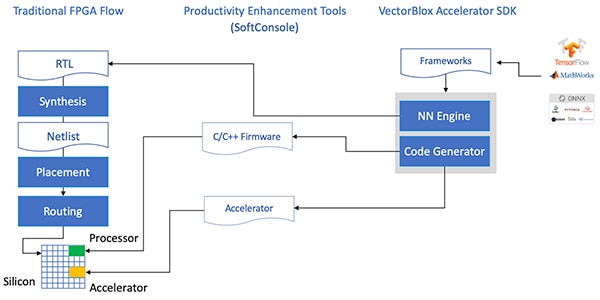

Ontwikkelingsflow vereenvoudigt NN FPGA-implementatie

Microchip schermt ontwikkelaars af van de complexiteit van het implementeren van een NN-conferentiemodel op PolarFire FPGA's. In plaats van de details van de traditionele FPGA-stroom te behandelen, werken de NN-modelontwikkelaars zoals gebruikelijk met hun NN-kaders en laden ze het resulterende model in de VectorBlox Accelerator Software Development Kit (SDK) van Microchip Technology. De SDK genereert de vereiste set bestanden, inclusief die welke nodig zijn voor de normale FPGA-ontwikkelingsflow en de eerder genoemde firmware- en netwerk-BLOB-bestanden (Afbeelding 7).

Afbeelding 7: De VectorBlox Accelerator SDK beheert de details van de implementatie van een NN-model op een FPGA, waarbij automatisch bestanden worden gegenereerd die nodig zijn om het op FPGA gebaseerde inferentiemodel te ontwerpen en uit te voeren. (Bron afbeelding: Microchip Technology)

Afbeelding 7: De VectorBlox Accelerator SDK beheert de details van de implementatie van een NN-model op een FPGA, waarbij automatisch bestanden worden gegenereerd die nodig zijn om het op FPGA gebaseerde inferentiemodel te ontwerpen en uit te voeren. (Bron afbeelding: Microchip Technology)

Omdat de VectorBlox Accelerator SDK flow het NN-ontwerp overlapt op de NN-motor die in de FPGA is geïmplementeerd, kunnen verschillende NN's op hetzelfde FPGA-ontwerp draaien zonder dat de FPGA-ontwerpsyntheseflow opnieuw hoeft te worden uitgevoerd. Ontwikkelaars maken C/C++ code aan voor het resulterende systeem en zijn in staat om modellen binnen het systeem 'on the fly' te wisselen of modellen tegelijkertijd te laten draaien met behulp van time slicing.

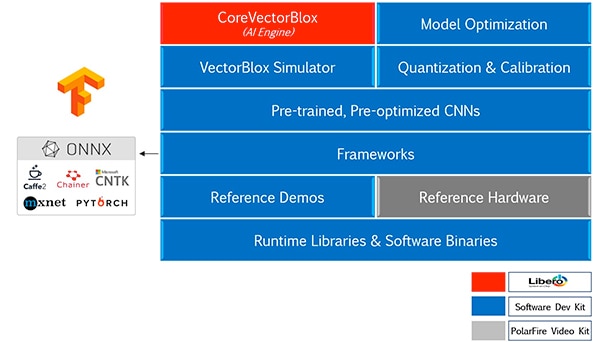

De VectorBlox Accelerator SDK smelt de Microchip Technology Libero FPGA-ontwerpsuite met een uitgebreide reeks mogelijkheden voor de ontwikkeling van NN-conferentiemodellen. Samen met modeloptimalisatie, kwantisatie en kalibratiediensten biedt de SDK een NN-simulator waarmee ontwikkelaars dezelfde BLOB-bestanden kunnen gebruiken om hun model te evalueren voorafgaand aan het gebruik ervan in de FPGA-hardware-implementatie (Afbeelding 8).

Afbeelding 8: De VectorBlox Accelerator SDK biedt een uitgebreide set van diensten die ontworpen zijn om de FPGA-implementatie van framework-generated inferentiemodellen te optimaliseren. (Bron afbeelding: Microchip Technology)

Afbeelding 8: De VectorBlox Accelerator SDK biedt een uitgebreide set van diensten die ontworpen zijn om de FPGA-implementatie van framework-generated inferentiemodellen te optimaliseren. (Bron afbeelding: Microchip Technology)

De VectorBlox Accelerator SDK ondersteunt modellen in Open Neural Network Exchange (ONNX) formaat en modellen uit een aantal frameworks waaronder TensorFlow, Caffe, Chainer, PyTorch en MXNET. Ondersteunde CNN-architecturen zijn MNIST, MobileNet-versies, ResNet-50, Tiny Yolo V2 en Tiny Yolo V3. Microchip werkt aan het uitbreiden van de ondersteuning om de meeste netwerken in de open-source OpenVINO toolkit open model zoo van voorgetrainde modellen, waaronder Yolo V3, Yolo V4, RetinaNet, en SSD-MobileNet, onder vele anderen, op te nemen.

Videokit demonstreert FPGA-inferentie

Om ontwikkelaars te helpen snel te evolueren naar de ontwikkeling van slimme ingebedde vision-toepassingen, biedt Microchip Technology een uitgebreide voorbeeldtoepassing die ontworpen is om te draaien op de MPF300-VIDEO-KITvan het bedrijf PolarFire FPGA Video en Imaging Kit en referentie-ontwerp.

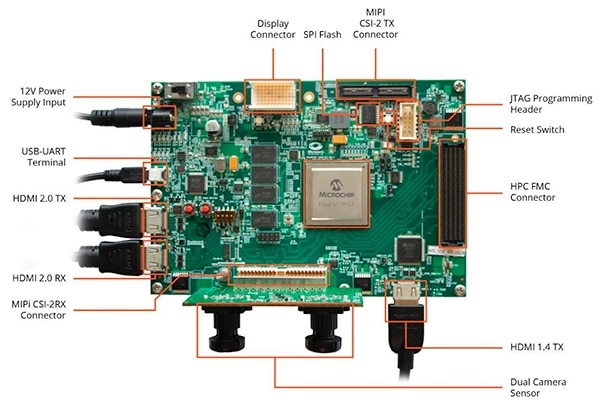

Gebaseerd op de Microchip MPF300T PolarFire FPGA, combineert het bord van de kit een dubbele camerasensor, dubbele datasnelheid 4 (DDR4) RAM, flash-geheugen, energiebeheer en een verscheidenheid aan interfaces (afbeelding 9).

Afbeelding 9: De MPF300-VIDEO-KIT PolarFire FPGA Video and Imaging Kit en de bijbehorende software bieden ontwikkelaars een snelle start met FPGA-gebaseerde gevolgtrekkingen in slimme ingebedde vision-toepassingen. (Bron afbeelding: Microchip Technology)

Afbeelding 9: De MPF300-VIDEO-KIT PolarFire FPGA Video and Imaging Kit en de bijbehorende software bieden ontwikkelaars een snelle start met FPGA-gebaseerde gevolgtrekkingen in slimme ingebedde vision-toepassingen. (Bron afbeelding: Microchip Technology)

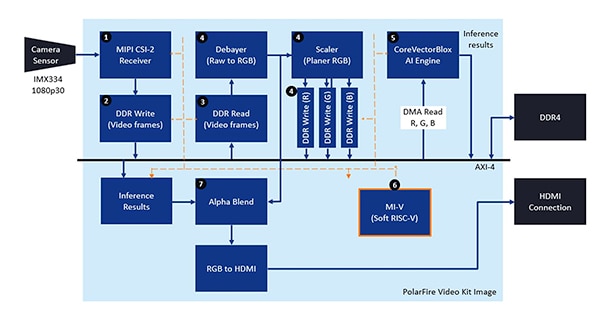

De kit wordt geleverd met een compleet Libero ontwerpproject dat wordt gebruikt om de firmware en de BLOB-bestanden voor het netwerk te genereren. Na het programmeren van de BLOB-bestanden in het ingebouwde flashgeheugen, klikken de ontwikkelaars op de run-knop in Libero om de demonstratie te starten, die de videobeelden van de camerasensor verwerkt en de inferentie-resultaten op een display weergeeft (Afbeelding 10).

Afbeelding 10: De Microchip Technology PolarFire FPGA Video en Imaging Kit laat zien hoe je een FPGA-implementatie van een slim ingebedde visiesysteem kunt ontwerpen en gebruiken, gebouwd rond de Microchip CoreVectorBlox NN-motor. (Bron afbeelding: Microchip Technology)

Afbeelding 10: De Microchip Technology PolarFire FPGA Video en Imaging Kit laat zien hoe je een FPGA-implementatie van een slim ingebedde visiesysteem kunt ontwerpen en gebruiken, gebouwd rond de Microchip CoreVectorBlox NN-motor. (Bron afbeelding: Microchip Technology)

Voor elke input-videoframe voert het op FPGA gebaseerde systeem de volgende stappen uit (met stapnummers die overeenkomen met Afbeelding 10):

- Laadt een frame van de camera

- Bewaar het frame in RAM

- Lees het frame van RAM

- Zet het ruwe beeld om in RGB, schaaf RGB en sla het resultaat op in RAM

- De Mi-V zachte RISC-V processor start de CoreVectorBlox engine, die het beeld uit het RAM haalt, gevolgtrekkingen maakt en de resultaten van de classificatie waarschijnlijkheid terug naar het RAM opslaat

- De Mi-V gebruikt de resultaten om een overlay frame te maken met bounding boxes, classificatieresultaten en andere meta-data en slaat het frame op in RAM

- Het originele frame wordt gemengd met het overlayframe en naar het HDMI-display geschreven

De demonstratie ondersteunt acceleratie van Tiny Yolo V3- en MobileNet V2-modellen, maar ontwikkelaars kunnen andere SDK-ondersteunde modellen uitvoeren met behulp van de eerder beschreven methoden door een kleine codewijziging door te voeren om de modelnaam en de metadata toe te voegen aan de bestaande lijst met de twee standaardmodellen.

Conclusie

AI-algoritmen zoals NN-modellen leggen doorgaans een rekenintensieve werklast op die meer robuuste computerhulpmiddelen vereist dan die welke beschikbaar zijn bij processoren voor algemene doeleinden. Hoewel FPGA's goed zijn uitgerust om te voldoen aan de prestatie- en lage vermogenseisen van de uitvoering van het inferentiemodel, kunnen conventionele FPGA-ontwikkelingsmethoden complex lijken, waardoor ontwikkelaars zich vaak tot suboptimale oplossingen wenden.

Zoals aangetoond, kunnen ontwikkelaars zonder FPGA-ervaring met behulp van gespecialiseerde IP en software van Microchip Technology op gevolgtrekkingen gebaseerde ontwerpen implementeren die beter voldoen aan de eisen op het gebied van prestaties, vermogen en ontwerpschema's.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.