Grondbeginselen van de FPGA's - Deel 4: Aan de slag met Xilinx FPGA's

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2020-04-01

Noot van de redactie: Optimale verwerkingsoplossingen worden vaak geleverd door combinaties van RISC, CISC, grafische processors en FPGA's; FPGA's op zichzelf; of door FPGA's die harde processorkernen als onderdeel van hun stof hebben. Veel ontwerpers zijn echter niet bekend met de mogelijkheden van FPGA's, hoe ze zijn geëvolueerd en hoe ze deze moeten gebruiken. Deel 1 van deze meerdelige serie biedt een introductie op hoog niveau van FPGA's; deel 2 richtte zich op het FPGA-aanbod van Lattice Semiconductor; en deel 3 concentreerde zich op de FPGA-apparaatfamilies en ontwerphulpmiddelen van Microchip Technology (van haar dochtermaatschappij Microsemi Corporation). Hier, in deel 4, worden de componenten en gereedschappen van Xilinx besproken. In deel 5 wordt het aanbod van Altera behandeld.

Zoals besproken in deel 1, hebben veldprogrammeerbare gate arrays (FPGA's) veel kenmerken die ze tot een onschatbare rekentool maken, hetzij stand-alone, hetzij in een heterogene architectuur, maar veel ontwerpers zijn niet bekend met FPGA's en hoe ze deze apparaten in hun ontwerpen moeten integreren.

Een manier om deze belemmering te overwinnen is om dieper te kijken naar FPGA-architecturen en bijbehorende tools van grote leveranciers; dit artikel kijkt naar de line-up van Xilinx.

Overzicht van high-level FPGA-opties

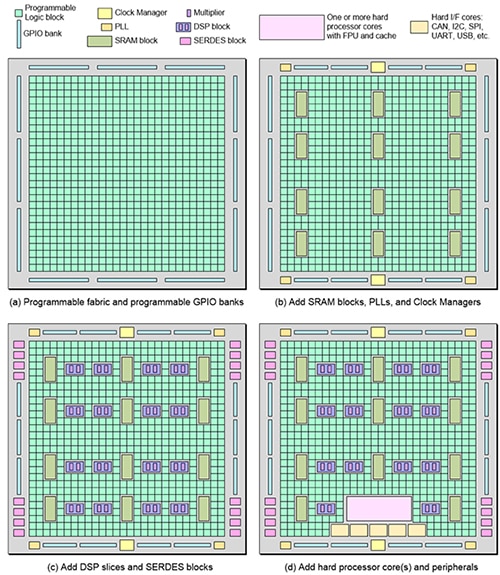

Er zijn veel verschillende soorten FPGA’s op de markt, elk met een andere combinatie van mogelijkheden en functies. De kern van elke FPGA is de programmeerbare stof. Dit wordt gepresenteerd als een reeks programmeerbare logische blokken, ook wel bekend als logische elementen (LE's) (Afbeelding 1a). De volgende stap in de FPGA-stof is het opnemen van zaken als blokken SRAM, genaamd blok RAM (BRAM), fase lock loops (PLL's), en klokmanagers (figuur 1b). Digitale signaalverwerking (DSP) blokken (genaamd DSP slices) en high-speed serializer/deserializer (SERDES) blokken kunnen ook worden toegevoegd (Afbeelding 1c).

Afbeelding 1: De eenvoudigste FPGA's bevatten alleen programmeerbare stof en configureerbare IO (GPIO) (a); verschillende architecturen vergroten deze fundamentele stof met SRAM-blokken, PLL's en klokmanagers (b); DSP-blokken en SERDES-interfaces (c); en harde processorkernen en randapparatuur (d). (Bron afbeelding: Max Maxfield)

Afbeelding 1: De eenvoudigste FPGA's bevatten alleen programmeerbare stof en configureerbare IO (GPIO) (a); verschillende architecturen vergroten deze fundamentele stof met SRAM-blokken, PLL's en klokmanagers (b); DSP-blokken en SERDES-interfaces (c); en harde processorkernen en randapparatuur (d). (Bron afbeelding: Max Maxfield)

Perifere interfacefuncties zoals CAN, I2C, SPI, UART en USB kunnen als zachte kernen in de programmeerbare infrastructuur worden geïmplementeerd, maar veel FPGA’s bevatten ze als harde kernen in het silicium. Op vergelijkbare wijze kunnen microprocessors als zachte kernen in de programmeerbare infrastructuur of als harde kernen in silicium worden geïmplementeerd (Afbeelding 1d). FPGA's met hard processorkernen worden system-on-chip (SoC) FPGA's genoemd. Verschillende FPGA’s bieden verschillende functies, eigenschappen, mogelijkheden en capaciteiten, gericht op verschillende markten en toepassingen.

Er zijn een aantal FPGA-leveranciers, waaronder Altera (die werd overgenomen door Intel), Atmel (die werd overgenomen door Microchip Technology), Efinix, Lattice Semiconductor, Microsemi (die ook werd overgenomen door Microchip Technology), en Xilinx.

Al deze verkopers hebben meerdere families van FPGA's; sommige bieden SoC FPGA's, sommige bieden apparaten aan die gericht zijn op kunstmatige intelligentie (AI) en machinaal leren (ML) toepassingen, en sommige bieden stralingsbestendige apparaten die gericht zijn op omgevingen met hoge straling, zoals de ruimte. Het kiezen van een component voor een betreffende taak kan lastig zijn, omdat er zoveel families zijn die elk verschillende functies bieden.

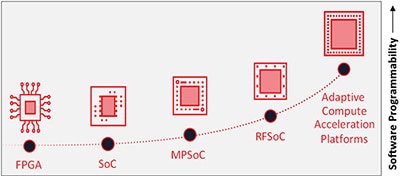

Introductie van Xilinx FPGA's, SoC's, MPSoC's, RFSoC's en ACAP's

De prestaties en mogelijkheden van het programmeerbare apparaataanbod van Xilinx gaan van bescheiden tot extreem hoog. Van traditionele FPGA's, tot SoC's (FPGA-programmeerbare stof met een enkele hardcore processor), MPSoC's (FPGA-programmeerbare stof met een meervoudige hardcore processor), RFSoC's (MPSoC's met RF-capaciteit) en ACAP's (Adaptive Compute Acceleration Platforms) (afbeelding 2).

Afbeelding 2: In de loop van de tijd is het Xilinx-architectuurportfolio geëvolueerd van eenvoudige FPGA's die alleen programmeerbare stof bevatten, naar SoC-apparaten waarin de programmeerbare stof is uitgebreid met een hardcore processor, naar MPSoC's met meerdere processoren, naar RF-SoC's met RF-mogelijkheden, naar de nieuwste generatie ACAP's, die gericht zijn op toepassingen als AI. (Bron afbeelding: Max Maxfield)

Afbeelding 2: In de loop van de tijd is het Xilinx-architectuurportfolio geëvolueerd van eenvoudige FPGA's die alleen programmeerbare stof bevatten, naar SoC-apparaten waarin de programmeerbare stof is uitgebreid met een hardcore processor, naar MPSoC's met meerdere processoren, naar RF-SoC's met RF-mogelijkheden, naar de nieuwste generatie ACAP's, die gericht zijn op toepassingen als AI. (Bron afbeelding: Max Maxfield)

Xilinx heeft zo'n uitgebreid productportfolio, richt zich op zoveel marktsegmenten en biedt zo'n breed scala aan implementatiemethoden dat het voor iemand die nieuw is in FPGA's een uitdaging kan zijn om het "grote geheel" te begrijpen.

In het geval van de markten van Xilinx-adressen, maar is niet beperkt tot, datacenters (compute, netwerk, opslag); communicatie (bedraad, draadloos); lucht-en ruimtevaart en defensie; industriële, wetenschappelijke en medische (ISM); test, meting, en emulatie (TME); en automotive, broadcast, en de consument.

In het geval van deploymentmethoden zijn dit onder andere wat Xilinx Hardware Adaptable Devices noemt, waaronder chips, evaluatieborden en ontwikkelingssets; Deployable End-Systems, waaronder system-on-modules (SoMs) en PCIe-versnellerkaarten; en FPGA as a service (FAAS), waaronder het evalueren en benutten van Xilinx-technologieën via toonaangevende cloudproviders, waaronder Amazon Web Services (AWS), Alibaba.com en Nimbix.net.

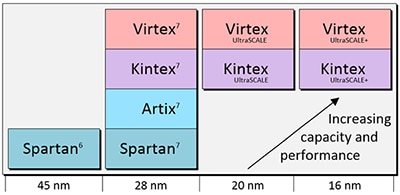

Met betrekking tot het Xilinx FPGA-aanbod, is een manier om deze te categoriseren door de procestechnische knoop (Afbeelding 3).

Afbeelding 3: Het Xilinx FPGA-aanbod biedt een uitgebreide portefeuille met meerdere knooppunten om tegemoet te komen aan de eisen van een breed scala aan toepassingen. (Bron afbeelding: Max Maxfield)

Afbeelding 3: Het Xilinx FPGA-aanbod biedt een uitgebreide portefeuille met meerdere knooppunten om tegemoet te komen aan de eisen van een breed scala aan toepassingen. (Bron afbeelding: Max Maxfield)

Afhankelijk van de doeltoepassing kunnen ontwerpers kiezen voor een goedkope, kleine FPGA-voetafdruk die op een eerder technologieknooppunt is geïmplementeerd, of in het geval van een geavanceerde netwerktoepassing, bijvoorbeeld, kiezen voor een apparaat met hoge capaciteit, hoge bandbreedte en hoge prestaties dat op een recenter technologieknooppunt is geïmplementeerd.

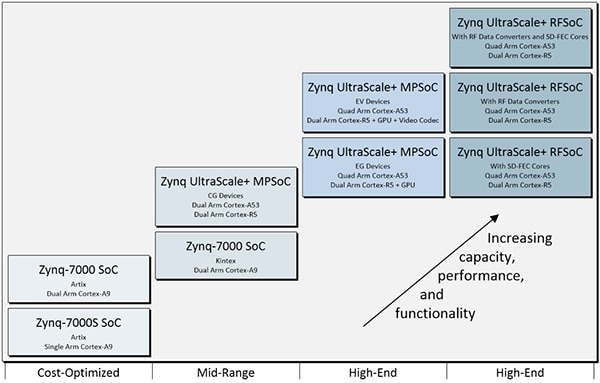

In het geval van ontwerpen die een of meer harde processorkernen nodig hebben (en andere geharde functies zoals GPU's, codecs, en soft decision, forward error correction (SD-FEC) cores), biedt Xilinx een portfolio van apparaten aan onder de overkoepelende naam Zynq. Een samenvatting van het Zynq SoC-, MPSoC- en RFSoC-aanbod is te zien in Afbeelding 4. Deze reeks oplossingen biedt ontwerpers een breed scala aan mogelijkheden om optimalisatie voor vermogen, prestaties, kosten en time-to-market te vergemakkelijken.

Afbeelding 4: Xilinx SoC, MPSoC, en RFSoC-aanbiedingen integreren de softwarematige programmeerbaarheid van een processor met de hardwarematige programmeerbaarheid van een FPGA, waardoor ontwerpers over systeemprestaties, flexibiliteit en schaalbaarheid beschikken. (Bron afbeelding: Maxfield)

Afbeelding 4: Xilinx SoC, MPSoC, en RFSoC-aanbiedingen integreren de softwarematige programmeerbaarheid van een processor met de hardwarematige programmeerbaarheid van een FPGA, waardoor ontwerpers over systeemprestaties, flexibiliteit en schaalbaarheid beschikken. (Bron afbeelding: Maxfield)

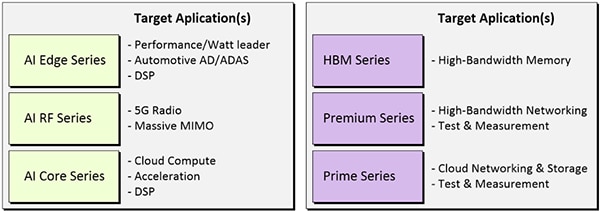

Het meest recente Xilinx-aanbod is het Versal Adaptive Compute Acceleration Platform (ACAP), dat allemaal is geïmplementeerd op het knooppunt van 7 nanometer (nm) procestechnologie. ACAP's zijn sterk geïntegreerde, multicore-rekenplatforms die zich kunnen aanpassen aan evoluerende en uiteenlopende algoritmen. Ze zijn dynamisch aanpasbaar op hard- en softwareniveau, zodat ze geschikt zijn voor een breed scala aan toepassingen en werklasten. De ACAP's zijn gearchiveerd rond een programmeerbare netwerk-on-chip (NoC) en kunnen eenvoudig worden geprogrammeerd door zowel hardware-ontwerpers als software-ontwikkelaars.

Nieuwe functies in de Versal-apparaten zijn onder andere intelligente engines (een enorme reeks vectorprocessoren voor ML- en DSP-werklasten); een hoge bandbreedte, lage latentie en een laag vermogen programmeerbare NoC die terabytes aan gegevens kan verplaatsen; en een geïntegreerde schil die verbeterde prestaties, gebruik en productiviteit biedt met een vooraf gebouwde kerninfrastructuur en systeemconnectiviteit.

Een overzicht van de Versal ACAP-portefeuille is te zien in Afbeelding 5.

Afbeelding 5: Xilinx Versal ACAP's zijn sterk geïntegreerde, multicore-computerplatforms die zich kunnen aanpassen aan evoluerende en uiteenlopende algoritmen. ACAP's zijn dynamisch aanpasbaar op hard- en softwareniveau, zodat ze geschikt zijn voor een breed scala aan toepassingen en werklasten. (Bron afbeelding: Max Maxfield)

Afbeelding 5: Xilinx Versal ACAP's zijn sterk geïntegreerde, multicore-computerplatforms die zich kunnen aanpassen aan evoluerende en uiteenlopende algoritmen. ACAP's zijn dynamisch aanpasbaar op hard- en softwareniveau, zodat ze geschikt zijn voor een breed scala aan toepassingen en werklasten. (Bron afbeelding: Max Maxfield)

Zoals zal worden besproken in het hoofdstuk over ontwerphulpmiddelen, is een belangrijke onderscheidende factor bij de Versal-apparaten een nieuwe softwarestack die gericht is op datawetenschappers en software-ingenieurs, maar ook op traditionele hardware-ontwerpingenieurs.

Er zijn nu talloze Xilinx-apparaten beschikbaar. Enkele voorbeelden zijn een Artix-7 FPGA, een Kintex UltraScale FPGA, een Kintex UltraScale+ FPGA, een Zynq-7000 SoC Module van Trenz Electronic GmbH en een Zynq UltraScale+ MPSoC.

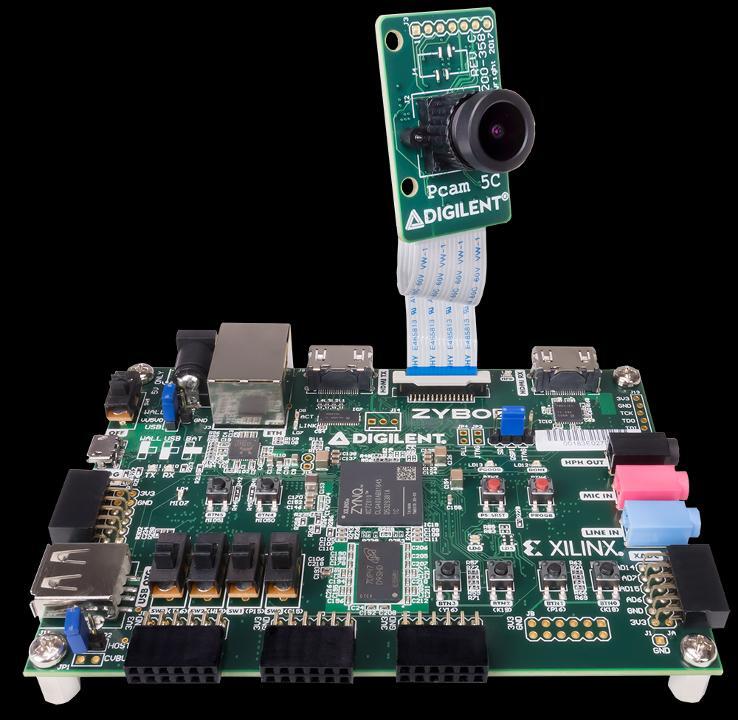

Ook is er een grote verscheidenheid aan evaluatie- en ontwikkelingsraden beschikbaar. Enkele voorbeelden zijn een Artix-7 FPGA Evaluation Board van Digilent, een Kintex UltraScale FPGA Evaluation Board van Analog Devices, een Kintex UltraScale+ FPGA Evaluation Board van Xilinx, een Zynq-7000 SoC FPGA Evaluation Board van Digilent, en een Zynq UltraScale+ MPSoC FPGA Evaluation Board, eveneens van Xilinx.

Ontwerp en ontwikkeling met Xilinx FPGA's, SoC's en ACAP's

Een gebied waar Xilinx zich echt onderscheidt van de concurrentie is in de breedte en diepte van de ontwerptools en -flows.

In deel 1 van deze serie over FPGA's merkten we op dat de traditionele manier om deze apparaten te ontwerpen is dat ingenieurs een hardwarebeschrijvingstaal (HDL) zoals Verilog of VHDL gebruiken om de bedoeling van het ontwerp vast te leggen op een abstractieniveau dat bekend staat als het registeroverdrachtsniveau (RTL). Deze RTL-beschrijvingen kunnen eerst worden gesimuleerd om te controleren of ze naar behoren functioneren, waarna ze worden doorgegeven aan een synthesegereedschap dat het configuratiebestand genereert dat wordt gebruikt om de FPGA te programmeren.

De volgende stap in de abstractie is het vastleggen van de bedoeling van het ontwerp met behulp van een programmeertaal zoals C/C++, of een speciale implementatie zoals SystemC, wat een set van C++ klassen en macro's is die een gebeurtenisgestuurde simulatie-interface bieden. Deze vergemakkelijken de simulatie van gelijktijdige processen, elk beschreven met behulp van de gewone C++ syntaxis. Dergelijke beschrijvingen kunnen worden geanalyseerd en geprofileerd door ze als gewone programma's uit te voeren, waarna ze worden doorgegeven aan een high-level synthese-engine (HLS), die RTL uitvoert die in de gewone synthese-engine wordt ingevoerd.

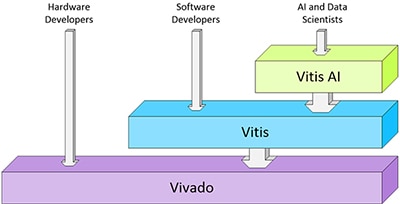

Al deze functionaliteit wordt omarmd door de Vivado Design Suite HLx Editions, waarvan de output de configuratiebitstream is die in de gerichte FPGA-, SoC-, MPSoC-, RFSoC- of ACAP-apparaten wordt geladen. Naast de mogelijkheid voor hardware-ontwikkelaars om gebruik te maken van C-gebaseerd ontwerp en geoptimaliseerd hergebruik, biedt Vivado ook IP-subsysteemhergebruik, integratie-automatisering en versnelde ontwerpsluiting (Afbeelding 6).

Afbeelding 6: Een overzicht op hoog niveau van de Xilinx Vivado- en Vitis-ontwerptoolstapel geeft weer hoe gebruikers met de tools kunnen werken op de meest geschikte abstractieniveaus. Hardwareontwerpers werken met Vivado, softwareontwikkelaars werken met Vitis, en AI en datawetenschappers werken met Vitis AI. (Bron afbeelding: Max Maxfield)

Afbeelding 6: Een overzicht op hoog niveau van de Xilinx Vivado- en Vitis-ontwerptoolstapel geeft weer hoe gebruikers met de tools kunnen werken op de meest geschikte abstractieniveaus. Hardwareontwerpers werken met Vivado, softwareontwikkelaars werken met Vitis, en AI en datawetenschappers werken met Vitis AI. (Bron afbeelding: Max Maxfield)

Het volgende abstractieniveau wordt ondersteund door het Vitis Unified Software Platform, dat softwareontwikkelaars de mogelijkheid biedt om naadloos versnelde applicaties te bouwen. Conceptueel "zitten op de top" is Vitis van Vitis AI, waardoor AI- en datawetenschappers kunnen werken op het TensorFlow-niveau van abstractie. Vitis AI is een ontwikkelingsplatform voor AI-inferentie op Xilinx-hardware-platforms, waaronder zowel edge-apparaten als Alveo PCIe-kaarten. Het bestaat uit geoptimaliseerde IP, tools, bibliotheken, modellen en voorbeeldontwerpen, en is ontworpen om het volledige potentieel voor AI-versnelling op Xilinx FPGA- en ACAP-apparaten te benutten.

Vitis AI voedt zich met Vitis, die op zijn beurt weer met Vivado. De belangrijkste afhaalmogelijkheid van Afbeelding 6 is dat gebruikers alleen "zien" wat ze nodig hebben om te "zien". Dat wil zeggen, hardware-ontwikkelaars zullen alleen Vivado "zien", software-ontwikkelaars zullen alleen Vitis "zien", en AI en data wetenschappers zullen alleen Vitis AI "zien". Op deze manier kunnen gebruikers met de tools werken op de meest geschikte abstractieniveaus.

Door softwareontwikkelaars te voorzien van een toolsuite zoals Vitis, die hen isoleert van de onderliggende hardware, worden FPGA's opengesteld voor een veel grotere pool van ontwikkelaars. Door AI- en datawetenschappers te voorzien van een toolsuite zoals Vitis AI, die hen in staat stelt zich te concentreren op hun eigen abstractieniveau en hen te isoleren van de onderliggende software, worden FPGA's opnieuw opengesteld voor een nieuwe klasse van ontwikkelaars.

Door deze mogelijkheden te bieden, staat Xilinx in de voorhoede van een industriebrede push om FPGA-tools naar steeds hogere niveaus van ontwerpabstractie te tillen, waardoor ontwikkelaars gemakkelijker gebruik kunnen maken van de mogelijkheden van deze apparaten en deze kunnen integreren in hun volgende ontwerpen.

Conclusie

Optimale oplossingen voor verwerkingsontwerp worden vaak geboden door combinaties van processors en FPGA's, door FPGA's alleen of door FPGA's die beschikken over harde processorkernen als onderdeel van hun stof. Als technologie hebben FPGA's zich in de loop der jaren snel ontwikkeld en zijn ze in staat om aan veel ontwerpeisen te voldoen in termen van flexibiliteit, verwerkingssnelheid en vermogen, waardoor ze zeer nuttig zijn voor een breed scala aan toepassingen, van intelligente interfaces tot machinevisie en kunstmatige intelligentie.

Zoals te zien is, gaat het programmeerbare aanbod van Xilinx van bescheiden tot extreem hoog in termen van prestaties en mogelijkheden. Ze variëren van traditionele FPGA's, tot SoC's (FPGA-programmeerbare stof met een enkele hardcore processor), MPSoC's (FPGA-programmeerbare stof met een meervoudige hardcore processor), RF-SoC's (MPSoC's met RF-capaciteit) en ACAP's (Adaptive Compute Acceleration Platforms).

Om ontwerpers te helpen bij het maken van ontwerpen met deze apparaten, biedt Xilinx een reeks tools om te voldoen aan de behoeften van hardware-ontwikkelaars (Vivado), software-ontwikkelaars (Vitis) en AI en datawetenschappers (Vitis AI).

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.