Netwerkprestaties versnellen: De impact van RDMA over Converged Ethernet (RoCE)

2024-12-27

De snelle evolutie van rekenintensieve toepassingen heeft de behoefte aan snellere, efficiëntere en schaalbare netwerkoplossingen vergroot. Een van de meest innovatieve technologieën om aan deze vraag te voldoen is Remote Direct Memory Access (RDMA) over Converged Ethernet (RoCE). Deze baanbrekende technologie maakt directe gegevensoverdracht tussen systemen mogelijk zonder tussenkomst van de CPU, waardoor de latentie aanzienlijk wordt verminderd en de algehele systeemprestaties verbeteren. iWave, een vooraanstaand FPGA-ontwerpbedrijf, loopt voorop in deze vooruitgang en heeft een robuuste 100 G Ethernet-oplossing geïmplementeerd door AMD's ERNIC IP (Ethernet RDMA Network Interface Controller Intellectual Property) te integreren in hun portfolio van embedded computingmodules. Deze integratie zal de RDMA-mogelijkheden in krachtige toepassingen verbeteren.

Afbeelding 1: RoCE maakt directe gegevensoverdracht tussen systemen mogelijk zonder tussenkomst van de CPU, waardoor de latentie aanzienlijk wordt verminderd en de algehele systeemprestaties verbeteren. (Bron afbeelding: iWave)

Afbeelding 1: RoCE maakt directe gegevensoverdracht tussen systemen mogelijk zonder tussenkomst van de CPU, waardoor de latentie aanzienlijk wordt verminderd en de algehele systeemprestaties verbeteren. (Bron afbeelding: iWave)

RDMA over Converged Ethernet (RoCE) begrijpen

RDMA is een cruciale technologie die directe geheugenoverdracht tussen hosts of servers mogelijk maakt, waarbij de CPU wordt omzeild. Hierdoor kunnen CPU's zich concentreren op de uitvoering van toepassingen en gegevensverwerking, wat leidt tot aanzienlijke verbeteringen in netwerkprestaties, gekenmerkt door minder latentie, lagere CPU-belasting en meer bandbreedte - en dat alles op een kosteneffectieve manier. RoCE is een specifiek netwerkprotocol ontworpen om RDMA operaties over Ethernet netwerken te vergemakkelijken. Door gebruik te maken van de bestaande Ethernet-infrastructuur is RoCE een aantrekkelijke optie voor organisaties die hun prestaties willen verbeteren zonder hun huidige netwerkinstellingen te herzien.

Soorten RoCE

RoCE is onderverdeeld in twee verschillende versies op basis van de gebruikte netwerkadapter: RoCE v1 en RoCE v2.

- RoCE v1: Dit protocol maakt communicatie mogelijk tussen twee hosts die zich binnen hetzelfde Ethernet uitzenddomein (VLAN) bevinden. Het gebruikt Ethertype 0x8915 en beperkt standaard Ethernetframes tot 1500 bytes, terwijl het Ethernet jumboframes toestaat tot 9000 bytes.

- RoCE v2: Om de beperkingen van RoCE v1 aan te pakken, introduceert RoCE v2 verbeteringen in pakketinkapseling door IP- en UDP-headers op te nemen. Door deze aanpassing kan RoCE v2 naadloos functioneren over zowel Layer 2 (Data Link Layer) als Layer 3 (Network Layer) netwerken, waardoor Layer 3-routing en -schaalbaarheid over meerdere subnetten ondersteund wordt. Vaak aangeduid als Routable RoCE (RRoCE), voegt RoCE v2 ook ondersteuning voor IP-multicast toe, waardoor de toepasbaarheid verder verbreed wordt.

ERNIC IP: uitbreiding van RDMA-mogelijkheden

De ERNIC (Embedded RDMA enabled NIC) IP is een aanpasbare Ethernet RDMA Network Interface Controller IP core ontworpen voor naadloze integratie met AMD FPGA's, MPSoC's en soft MAC IP-implementaties. Deze oplossing wordt gekenmerkt door een hoge doorvoer, lage latentie en een volledig hardware-offloaded, betrouwbaar mechanisme voor gegevensoverdracht via standaard Ethernet. iWave heeft zijn toewijding aan technologische vooruitgang geïllustreerd door met succes een 100 G Ethernet-oplossing te implementeren. Deze prestatie werd mogelijk gemaakt door het gebruik van iWave's Zynq UltraScale+ MPSoC-ontwikkelkit, waarin AMD's ERNIC IP is geïntegreerd.

De Zynq UltraScale+ MPSoC-ontwikkelkit is speciaal ontwikkeld voor het maken van prototypes en het evalueren van 100G Ethernet-oplossingen, waarbij gebruik wordt gemaakt van snelle QSFP-28-connectors.

Demo instellen

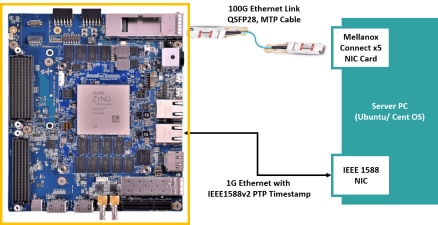

Een typische demo-opstelling (Figuur 2) bestaat uit:

- Zynq UltraScale+ MPSoC ZU19EG-ontwikkelkit van iWave

- Advantech Mellanox ConnectX-5 100G NIC

- Sync 1588 PTP ingeschakeld 1G NIC

- MTP-kabel, QSFP-28 modules en CAT6 RJ45 Ethernetkabel

- Ubuntu 22.04 server-pc

Afbeelding 2: De typische opstelling voor de Zynq UltraScale+ MPSoC-ontwikkelkit. (Bron afbeelding: iWave)

Afbeelding 2: De typische opstelling voor de Zynq UltraScale+ MPSoC-ontwikkelkit. (Bron afbeelding: iWave)

Overzicht systeemarchitectuur

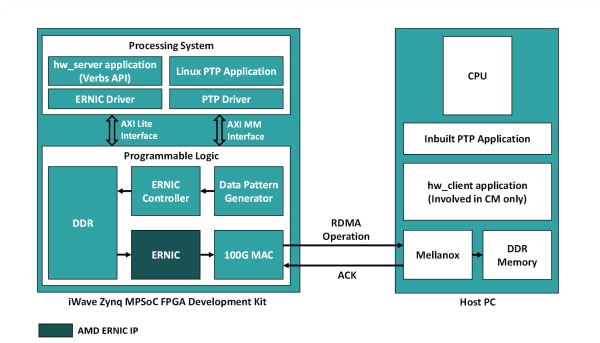

De systeemarchitectuur is ontworpen om gegevensoverdracht te optimaliseren, met duidelijk gedefinieerde rollen tussen het processysteem (PS) en de programmeerbare logica (PL) componenten. De implementatie beschikt ook over PTP-synchronisatie (precision time protocol), cruciaal voor real-time toepassingen. Met opmerkelijke prestatiecijfers, zoals de mogelijkheid om 8K-video te verwerken met meer dan 100 frames per seconde, strekken de potentiële toepassingen zich uit over verschillende sectoren, waaronder datacenters, multimedia en high-performance computing, wat de veelzijdigheid en het belang van de technologie in moderne computeromgevingen onderstreept.

De high-level architectuur van het systeem, weergegeven in figuur 3, benadrukt de verschillende rollen van de PS- en PL-componenten binnen de Zynq UltraScale+ MPSoC. De PS is voorzien van een ARM Cortex-A53-gebaseerde Hard SoC, die essentieel is voor systeemconfiguratie, besturing en diagnose. De belangrijkste onderdelen van deze architectuur zijn:

- 100 G Ethernet MAC-driver: Garandeert robuuste prestaties en gegevensoverdracht met lage latentie bij 100 Gb/s

- ERNIC-controllerdriver: Verantwoordelijk voor het beheren van inkomende data naar DDR en het faciliteren van communicatie tussen de gebruikerstoepassing en ERNIC IP door middel van efficiënte deurbeluitwisselingen

- RDMA kern- en gebruikersbibliotheken: Zorgt voor compatibiliteit en optimale prestaties voor RDMA-operaties in zowel kernel- als gebruikersruimten.

Afbeelding 3: De verschillende rollen van het verwerkingssysteem en de programmeerbare logica-componenten binnen de Zynq UltraScale+ MPSoC. (Bron afbeelding: iWave)

Afbeelding 3: De verschillende rollen van het verwerkingssysteem en de programmeerbare logica-componenten binnen de Zynq UltraScale+ MPSoC. (Bron afbeelding: iWave)

De AMD ERNIC IP zet de RoCE v2 stack effectief over op de FPGA, waarbij de ERNIC-controller de handshaking tussen de verschillende modules beheert om de gegevensoverdracht te vergemakkelijken. Het genereert items in de werkwachtrij en stuurt meldingen (deurbellen) naar de ERNIC IP. Tegelijkertijd beheert het 100 G Ethernet-subsysteem van de Zynq UltraScale+ MPSoC de MAC- en fysieke lagen, terwijl de gegevenspatroongenerator verantwoordelijk is voor het produceren van ruwe data en video datapatronen.

Precisietijdprotocol (PTP)

De PTP-tijdstempel (IEEE 1588 standaard) speelt een cruciale rol bij het synchroniseren van tijd tussen systemen in een Ethernet-netwerk. Deze synchronisatie is van vitaal belang voor het verbeteren van de prestaties van realtime toepassingen en maakt gesynchroniseerde gegevensuitwisselingen met een lage latentie op nanosecondenniveau mogelijk.

Belangrijkste hoogtepunten van de opstelling

De belangrijkste kenmerken van deze opstelling zijn:

- Implementatie van 100G Ethernet over RoCE v2 met behulp van AMD ERNIC IP

- Betrouwbaar verbindingstype

- RDMA SEND-, RDMA READ- en RDMA WRITE-functionaliteiten voor pakketverwerking

- Ondersteuning voor RDMA Send with Immediate en RDMA Write with Immediate-berichttypes

- Prestatietests voor RDMA met XRPING en PERFTEST-toepassingen

- Aangepaste gegevenspatroongenerator voor RAW- en videopatronen

- Invoegen van PTP-tijdstempels naast gegevens

De gedetailleerde doorvoerstatistieken voor de overdracht van videogegevens van de Zynq UltraScale+ MPSoC-ontwikkelkit naar de server-pc laten indrukwekkende prestaties zien, met de mogelijkheid om 8K-video met meer dan 100 fps en 4K-video met meer dan 400 fps te verwerken.

Potentiële toepassingen

De integratie van RDMA over Converged Ethernet en ERNIC IP opent nieuwe perspectieven in verschillende industrieën en zorgt voor een aanzienlijke verbetering van de connectiviteit, prestaties en efficiëntie in een reeks toepassingen, waaronder:

- Datacenters en cloudcomputing: Efficiënte servercommunicatie vergemakkelijken en gegevensverwerking versnellen in cloudarchitecturen

- Video/beeldopname en -overdracht: Gunstig voor multimediatoepassingen, uitzendingen en omgevingen met virtuele realiteit (VR)

- Opslagoplossingen: Snellere gegevensoverdracht mogelijk maken tussen opslagapparaten en servers, waardoor de prestaties van het opslagsysteem verbeteren.

- High-performance computing (HPC): Verbeteren van gegevensoverdrachtsnelheden en verminderen van latentie binnen HPC-clusters voor snellere rekentaken en simulaties.

- IoT edge-apparaten: Real-time gegevensverzameling en -overdracht van sensoren en apparaten mogelijk maken

Omdat de vraag naar snellere en efficiëntere oplossingen voor gegevensoverdracht blijft stijgen, zijn RDMA over Converged Ethernet en ERNIC IP klaar om een cruciale rol te spelen in de toekomst van high-performance computing.

Conclusie

iWave's uitgebreide portfolio van FPGA- en SoC FPGA-platforms, gecombineerd met zijn diepgaande technische expertise, stelt klanten in staat om baanbrekende producten te ontwikkelen die gebruikmaken van de nieuwste ontwikkelingen op het gebied van kunstmatige intelligentie (AI), machine learning en edgecomputing. Door samen te werken met iWave kunnen bedrijven hun productontwikkeling versnellen, risico's beperken en de concurrentie voorblijven in een steeds complexer technologisch landschap.

Neem voor meer informatie of om aangepaste vereisten te bespreken contact met ons op via mktg@iwave-global.com

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.