Zero-delay klokbuffers beoordelen en gebruiken om de timing te beschermen in synchrone digitale systemen

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2019-07-18

Naarmate de prestaties van digitale systemen verbeteren, moeten ontwerpers steeds zorgvuldiger aandacht besteden aan het ontwerp van de klokopwekkings- en -distributiecircuits om verschillen of onzekerheden in de klokdistributietiming te voorkomen. Dergelijke problemen kunnen de systeemprestaties aantasten, timingmarges verminderen of functionele fouten veroorzaken. Om timingproblemen door skew te voorkomen kunnen ontwerpers zero-delay klokbuffers gebruiken.

De typische synchrone digitale systemen gebruiken een normale klok om bewerkingen op volgorde te houden. Deze klok moet worden gedistribueerd naar alle opeenvolgende elementen om ervoor te zorgen dat het systeem met de gewenste snelheid blijft werken, waarbij vaak gesloten-lusregeling wordt gebruikt om timing-skew te verminderen. Zero-delay klokbuffers gebruiken fasevergrendelde lussen (phase-locked loops - PLL's) om te garanderen dat de gebufferde klokuitgangen worden uitgelijnd met de referentie-klokingang zodat er een vrijwel perfecte klok-timing wordt gegarandeerd.

In dit artikel worden zero-delay klokbuffers beschreven, wordt uitgelegd hoe ze werken met voorbeeldoplossingen van Cypress Semiconductor, Integrated Device Technology Inc. (IDT) en ON Semiconductor en wordt in detail beschreven hoe klok-skew onder controle kan worden gehouden. Er worden ook testmethoden in onderzocht om de stabiliteit van deze apparaten te verzekeren.

Klok-skew

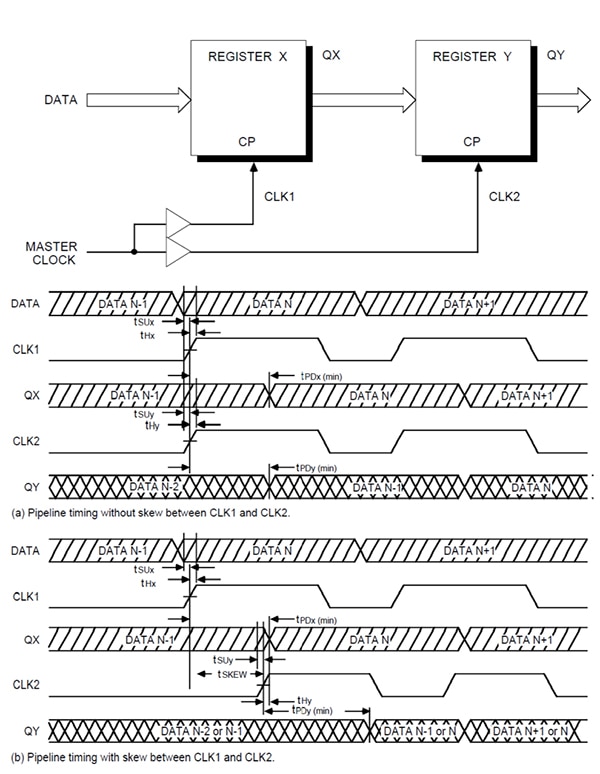

In synchrone digitale systemen kunnen de klokken op verschillende tijden in verschillende delen van het circuit aankomen, waardoor er klok-skew wordt veroorzaakt. Klok-skew kan timingmarges verminderen en uitval van het systeem veroorzaken (Afbeelding 1).

Afbeelding 1: Een eenvoudig voorbeeld van hoe kloktijd-skew bewerkingen van een pijplijnregister kan beïnvloeden. Een geskewde klok kan de setup schenden en/of vereisten vasthouden met een onbepaalde uitgangsstatus tot gevolg. (Bron afbeelding: IDT)

Afbeelding 1: Een eenvoudig voorbeeld van hoe kloktijd-skew bewerkingen van een pijplijnregister kan beïnvloeden. Een geskewde klok kan de setup schenden en/of vereisten vasthouden met een onbepaalde uitgangsstatus tot gevolg. (Bron afbeelding: IDT)

Denk aan een eenvoudig synchroon systeem dat uit twee registers bestaat. De data wordt door de registers gepijplijnd, zodat de uitgang van register X, QX, de ingang is voor register Y. Er worden klokken naar de registers gevoerd via onafhankelijke buffers en speciale CLK1 en CLK2. Als er geen skew is tussen de klokken, zoals te zien is in het schema (a), wordt de datastatus N, die voldoet aan de registersetup (tSUx) en de vasthoudtijdvereisten (tHx), in de register X-uitgang, QX, geklokt op de eerste klokflank na de propagatievertraging van het register. Dezelfde klokflank op CLK2 veroorzaakt dat de vorige status van QX, N-1, wordt gelezen door het register en verschijnt bij de uitgang QY na de propagatievertraging van het register.

Als er tijd-skew is tussen CLK1 en CLK2, zoals wordt getoond in schema (b), kan de status van QX in overgang zijn wanneer CLK2 optreedt. De ingang naar register Y voldoet mogelijk niet aan de setup- of vasthoudtijdvereisten van het register en de uitgang kan onbepaald zijn en tot een fout leiden.

Om minimale klok-skew te verzekeren, stemmen ontwerpers de lengte van printplaatsporen op elkaar af, selecteren ze buffers en andere klokcomponenten met gelijke propagatievertragingen en balanceren ze de belasting uit op de diverse klokbronnen. Hoewel die technieken helpen, is gewoonlijk het gebruik van zero-delay klokbuffers nodig om een goede controle over klok-skew te krijgen.

Klok-skew onder controle houden

Klok-skew ontstaat vanuit vele mogelijke bronnen. De meest voor de hand liggende bron is kloksignalen die over printplaatverbindingen met verschillende lengtes worden geleid. Andere skew-bronnen zijn klokken die door verschillende actieve apparaten met verschillende propagatievertragingen lopen, klokbuffers met verschillende belasting, of temperatuurverschillen in buffers. Terwijl sommige van die effecten onder controle kunnen worden gehouden, gebruiken ontwerpers vaak actieve apparaten om klokken opnieuw te synchroniseren met een referentieklok met gebruik van PLL's.

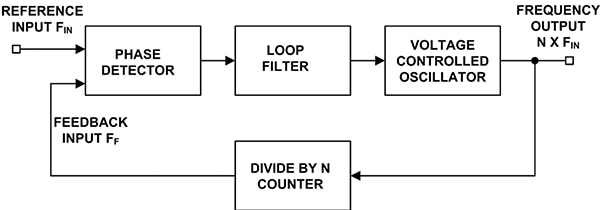

PLL-circuits worden gebruikt voor frequentie- en faseregeling. Ze kunnen worden geconfigureerd als frequentievermenigvuldigers, demodulators, volggenerators of circuit voor fasecorrectie. Voor al die toepassingen zijn verschillende kenmerken nodig, maar ze gebruiken allemaal hetzelfde basiscircuitconcept dat te zien is op Afbeelding 2.

Afbeelding 2: Blokdiagram van een PLL die is geconfigureerd als frequentievermenigvuldiger. Dit is in feite een feedbackregelsysteem dat de fase van een oscillator met geregelde spanning (voltage controlled oscillator - VCO) regelt. (Bron afbeelding: DigiKey)

Afbeelding 2: Blokdiagram van een PLL die is geconfigureerd als frequentievermenigvuldiger. Dit is in feite een feedbackregelsysteem dat de fase van een oscillator met geregelde spanning (voltage controlled oscillator - VCO) regelt. (Bron afbeelding: DigiKey)

Op afbeelding 2 staat een blokdiagram van een basis-PLL die is geconfigureerd als frequentievermenigvuldiger. De werking van dit circuit is kenmerkend voor alle PLL's. Het is in feite een feedbackregelsysteem dat de fase van een VCO regelt. Het ingangssignaal wordt toegepast op één ingang van een fasedetector. De andere ingang is een feedbacksignaal van de uitgang van een gedeeld-door-N-teller. Gewoonlijk zijn de frequenties van beide signalen bijna hetzelfde.

De uitgang van de fasedetector is een spanning die evenredig is met het faseverschil tussen de twee ingangen. Dit signaal wordt toegepast op het lusfilter. Het lusfilter bepaalt de dynamische kenmerken van de PLL. Het gefilterde signaal regelt de VCO. De uitgang van de VCO heeft een frequentie van N maal de ingang die aan de frequentiereferentie-ingang (FIN) wordt geleverd. Dit uitgangssignaal wordt teruggestuurd naar de fasedetector via de gedeeld-door-N-teller.

Gewoonlijk wordt het lusfilter zo ontworpen dat het bij de kenmerken past die nodig zijn voor de toepassing van de PLL. Als de PLL dient voor het verwerven en traceren van een signaal, is de bandbreedte van het lusfilter groter dan als de PLL een vaste ingangsfrequentie zou verwachten. Het frequentiebereik dat de PLL accepteert en vasthoudt wordt het vangbereik genoemd. Wanneer de PLL is vergrendeld en een signaal traceert, wordt het bereik met frequenties die de PLL volgt het volgbereik genoemd. Gewoonlijk is het volgbereik groter dan het vangbereik. Het PLL-lusfilter bepaalt ook hoe snel de signaalfrequentie kan veranderen en toch de vergrendeling kan behouden. Dit is de maximale variatiesnelheid. Hoe nauwer de bandbreedte van het lusfilter, hoe kleiner de bereikbare fasefout. Dit gaat wel ten koste van een langzamere reactie en een verminderd vangbereik. PLL's die worden gebruikt in kloktoepassingen werken voornamelijk met vaste frequenties.

Zero-delay klokbuffers

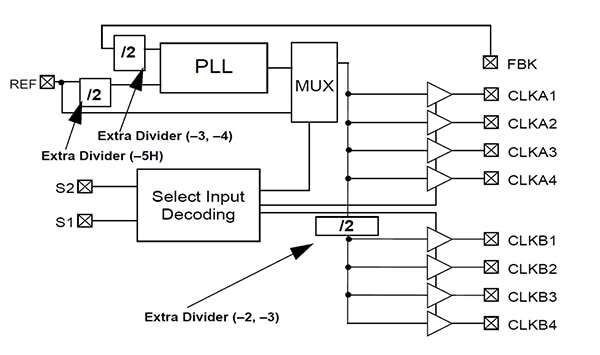

Een zero-delaybuffer is een apparaat dat een kloksignaal kan bufferen, door meerdere klokuitgangen te produceren van een enkele referentieklokingang. De meerdere, gebufferde klokuitgangen hebben weinig tot geen vertraging ten opzichte van de referentieklokingang en een lage skew tussen de uitgangen. Het vereenvoudigde blokdiagram van een Cypress Semiconductor CY2308SXC-3T zero-delaybuffer wordt getoond in Afbeelding 3.

Afbeelding 3: De CY2308SXC-3T zero-delaybuffer met acht uitgangen gebruikt een PLL om alle uitgangen te synchroniseren op een tijd-skew van bijna nul. (Bron afbeelding: Cypress Semiconductor)

Afbeelding 3: De CY2308SXC-3T zero-delaybuffer met acht uitgangen gebruikt een PLL om alle uitgangen te synchroniseren op een tijd-skew van bijna nul. (Bron afbeelding: Cypress Semiconductor)

Een zero-delaybuffer is gebouwd met een integrale PLL die een referentie-ingang (REF) en een feedback-ingang (FBK) accepteert als de ingangen voor de fasedetector. De feedbackingang wordt aangedreven door één van de door de gebruiker geselecteerde uitgangen. De interne fasedetector van de PLL past de uitgangsfase van de VCO aan, zodat de twee ingangen geen fase- of frequentieverschil hebben. Eén van de gebufferde klokuitgangen en zijn belasting wordt geselecteerd als feedbacksignaal naar de PLL via de fasedetector. Los van de belastingsveranderingen bij die uitgang blijft de PLL die uitgangsbelastingsveranderingen dynamisch compenseren met nul vertraging van de ingang naar de uitgang die feedback aanstuurt tot gevolg, los van de uitgangsbelasting.

De CY2308-familie heeft twee banken met vier uitgangen die werken over een frequentiebereik van 10 tot 133 megahertz (MHz). De ingang-naar-uitgang tijd-skew is minder dan 250 picoseconden (ps) en de klok-skew tussen de uitgangen is minder dan 200 ps. De ingang-naar-uitgang tijd-skew kan worden aangepast door de belastingscapaciteit op de uitgang die wordt gebruikt voor de feedbackingang te veranderen.

De productfamilie biedt diverse configuraties van delen-door-twee delers. De geselecteerde component is de "-3"-variant die twee van die delers heeft, zoals te zien is in het blokdiagram. Met deze configuratie kan de gebruiker uitgangen van twee- of viermaal de ingangsfrequentie van de referentieklok verkrijgen.

De meest algemeen gebruikte zero delay-buffer is geconfigureerd met vijf uitgangen en is verkrijgbaar bij meerdere verschillende fabrikanten. De Cypress Semiconductor CY2305SXI-1HT, de IDT 2305-1DCGI8 en de ON Semiconductor NB2305AI1HDR2G lijken erg veel op elkaar. Ze hebben allemaal vijf gebufferde klokuitgangen, een enkele CLKOUT-poort met een quad-bank met klokuitgangen. Anders dan met de CY2308 is het PLL-feedbackpunt vast op het enkele CLKOUT-signaal.

De dynamiek van zero delay-buffers

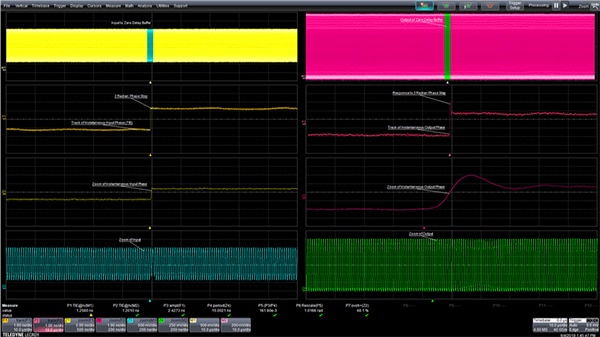

De PLL's in zero delay-buffers zijn in feite feedbackregelsystemen. De dynamiek wordt geregeld door het PLL-lusfilter. Zoals bij alle regelsystemen is het belangrijk om de feedbacklusdynamiek te beoordelen in reactie op een transiënte ingang. Eén manier om dat te doen, is een ingang met een stapverandering toe te passen om de stapresponsie te beoordelen (Afbeelding 4).

Afbeelding 4: De stapresponsie van de CY2305 zero delay-buffer beoordelen met een fasestap van 1 radiaal bij 66,67 MHz. Het raster linksboven is het ingangssignaal en het raster rechtsboven de uitgang. (Bron afbeelding: DigiKey)

Afbeelding 4: De stapresponsie van de CY2305 zero delay-buffer beoordelen met een fasestap van 1 radiaal bij 66,67 MHz. Het raster linksboven is het ingangssignaal en het raster rechtsboven de uitgang. (Bron afbeelding: DigiKey)

Het ingangssignaal is een 66,67 MHz sinus met een stap van één radiaal in het midden van het verkregen signaalvenster. Deze golfvorm wordt gegenereerd door een willekeurige golfvormgenerator (arbitrary waveform generator - AWG). Zowel de ingang als de uitgang van de CY2305 zero delay-buffer zijn verkregen met een oscilloscoop met een tijdbasisinstelling van 10 microseconden (µs) per schaaldeel.

Het raster linksboven in Afbeelding 4 is het ingangssignaal en het raster rechtsboven de uitgang. De tijdsintervalfout (time interval error - TIE) is het tijdsverschil van de gemeten klokflank tot zijn ideale positie en wordt gemeten voor iedere golfvorm. In wezen is dit de momentane fase van het signaal waarnaar wordt verwezen met een vaste kloksnelheid, in dit geval 66,67 MHz. De waarde van TIE voor iedere klokcyclus van zowel de ingang als de uitgang wordt uitgezet als een golfvorm die een TIE-spoor wordt genoemd. Het spoor voor de ingang is het tweede raster van boven aan de linkerkant. Hier is de stap in de fase zichtbaar met een amplitude van 2,4 nanoseconden (ns). Deze waarde vertegenwoordigt een faseverschuiving van één radiaal voor de klokfrequentie van 66,67 MHz.

Het tweede spoor van bovenaf aan de rechterkant is het TIE-spoor van de uitgang. Het spoor van de uitgang vertoont wat overshoot en stelt zich in op een nieuwe gemiddelde waarde die bij de ingangsverandering past. Het derde spoor van boven toont een horizontaal uitvergroot zoomspoor van de ingang aan de linkerkant en van de uitgang aan de rechterkant. De details van de ingangsstap laten een schone overgang zien.

De ingezoomde uitgang toont wat overshoot en stelt zich dan snel in op de nieuwe gemiddelde waarde in ongeveer één cyclus van ongeveer 500 ns lang. Dit is een goede stapresponsie voor zo'n grote fasestap. Deze stabiliseert snel en er is geen bewijs van een onstabiele oscillerende reactie.

De twee onderste sporen tonen horizontaal uitvergrote weergaven van de ingang (links) en de uitgang (rechts). De grote fasestap is duidelijk zichtbaar in de ingang, maar de langzame uitgangsresponsie is minder zichtbaar op deze tijdschaal.

Conclusie

Ontwerpers van digitale systemen met hoge prestaties moeten zorgvuldig aandacht besteden aan het ontwerp van de klokopwekkings- en -distributiecircuits om verschillen of onzekerheden in de klokdistributietiming te voorkomen. Dergelijke problemen kunnen de systeemprestaties aantasten, timingmarges verminderen of functionele fouten veroorzaken.

Zoals beschreven, is de zero delay-buffer een goed middel voor actieve regeling bij het propageren van meerdere kloksignalen en het behouden van de synchronisatie met een master-kloksignaal. Ze bieden een uitstekende tracering, zelfs met aanzienlijke belastingsveranderingen op de gedetecteerde uitgang. Zoals getoond, moeten ontwerpers echter zorgvuldig de feedbacklusdynamiek van een zero delay-buffer beoordelen om te garanderen dat die voldoet aan de eisen van de toepassing.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.