Het programmageheugen van een microcontroller uitbreiden met SPI XiP Flash - waarom en hoe

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2019-05-08

Naarmate microcontrollertoepassingen complexer worden, gebruiken ontwikkelaars meer Flash-programmageheugen voor de toepassingsfirmware. Dit geldt in het bijzonder voor Internet of Things (IoT)-eindpunten die relatief complexe edge computing beginnen uit te voeren. Soms kan de uitbreiding van toepassingen echter dusdanig zijn dat extern programmageheugen vereist is, en op dit punt moeten ontwikkelaars kiezen tussen parallel of serieel Flash-geheugen.

Toevoeging van een externe parallelle Flash-geheugenchip bezet I/O-lijnen, voegt complexiteit toe en neemt extra ruimte in beslag op het bord. In dit artikel wordt beschreven hoe het Flash-programmageheugen van een microcontroller kan worden uitgebreid door toevoeging van een externe seriële Flash-geheugenchip van Adesto Technologies die een SPI eXecute in Place (XiP)-interface ondersteunt. Ook wordt uitgelegd hoe XiP Flash in de geheugenruimte van een microcontroller van Microchip Technology wordt toegewezen zodat de code-uitvoering nagenoeg transparant is voor de firmware.

Redenen voor externe geheugenuitbreiding

Waar mogelijk zouden ontwikkelaars bij de ontwikkeling van een toepassing moeten beginnen met het kiezen van een microcontroller die een roadmap van pin-compatibele apparaten met meer geheugen heeft. Als gedurende de ontwikkeling de toepassingsfirmware dusdanig uitbreidt dat het Flash-geheugen op het targetapparaat niet meer toereikend is, kan in plaats daarvan een pin-compatibel apparaat met meer Flash worden gekozen gedurende de ontwikkeling. Zo kan het toepassingsgeheugen worden uitgebreid zonder dat het ontwerp van het pc-bord moet worden aangepast voor een andere microcontroller.

Het is echter mogelijk dat de toepassing meer programmageheugen nodig heeft dan op de chip voor een pin-compatibele microcontrollerfamilie beschikbaar is, waardoor gebruik van een Flash-geheugen buiten de chip noodzakelijk wordt. Dit komt steeds vaker voor en gebeurt om verschillende redenen, bijvoorbeeld:

- De systeemgrootte overstijgt het oorspronkelijke concept gedurende de ontwikkelingsfase. Dit kan te wijten zijn aan last-minute wijzigingen in de toepassing, het ongemerkt naar binnen sluipen van extra functies of doordat men niet accuraat heeft ingeschat hoeveel geheugen de toepassing nodig heeft. De mogelijkheden zijn ofwel een upgrade met een pin-compatibele microcontroller met meer Flash-programmageheugen ofwel toevoeging van extra extern Flash-programmageheugen, iets wat voor vertraging in het project kan zorgen als de ontwikkeling reeds in een vergevorderd stadium is.

- Toekomstige firmware-upgrades in het veld kunnen meer Flash-programmageheugen vereisen dan op de in het systeembord aanwezige microcontroller beschikbaar is. In deze situatie zijn de mogelijkheden beperkt: de systemen in het veld vervangen door systemen met meer Flash-programmageheugen of de upgrade annuleren.

- De ontwikkeling van de systeemproductfamilie kan een nieuw product vereisen dat meer Flash-programmageheugen nodig heeft dan reeds beschikbaar is voor de pin-compatibele microcontrollerfamilie. De opties zijn om het systeem opnieuw te ontwerpen en een nieuwe microcontrollerfamilie te gebruiken of om extern Flash-programmageheugen toe te voegen.

Het is natuurlijk belangrijk dat een ontwikkelaar op de behoeften van huidige en toekomstige systemen voor deze geheugenuitbreiding anticipeert en er in de planning rekening mee houdt. Als de mogelijkheid bestaat dat het project extern Flash-programmageheugen nodig zal hebben, dient de ontwikkelaar op het pc-bord alvast een plaats voor toekomstige uitbreiding te reserveren. Alhoewel het niet persé noodzakelijk is dat de Flash-geheugenchip op het bord wordt gemonteerd, kan men beter het zekere voor het onzekere nemen en alvast voldoende ruimte inplannen.

De traditionele manier om het Flash-programmageheugen uit te breiden was door een parallelle Flash-interface met adres en datalijnen te gebruiken. Maar zelfs bij het meest efficiënte gebruik van parallel Flash-geheugen, waarbij geen concessies worden gedaan voor wat betreft de snelheid, zijn 16 bit voor adressen, 16 bit voor gegevens en vier of meer stuursignalen nodig. Hiervoor zijn 36 of meer microcontrollerpinnen vereist.

Dit betekent niet alleen een inefficiënt gebruik van de microcontroller, maar beperkt ook de selectie van de microcontroller tot apparaten met een externe bus, waardoor het aantal pinnen van de microcontroller toeneemt. Een externe parallelle bus neemt ook veel ruimte in beslag op het pc-bord, en het hoge-snelheid adres en de databus verhogen de kans op elektromagnetische interferentie (EMI).

SPI XiP code-uitvoering

Een meer doeltreffende optie is gebruik te maken van een extern Flash-programmageheugenapparaat dat een SPI XiP-interface ondersteunt. Een SPI XiP-interface heeft maar zes pinnen nodig voor de interface met de hostmicrocontroller. Anders dan bij een conventionele SPI-interface, verloopt de toegang tot het geheugen op het externe Flash-geheugenapparaat niet rechtstreeks met een SPI-firmwaredriver, maar wordt toegewezen in het programmageheugen van de microcontroller.

Een goed voorbeeld van een serieel Flash-geheugenapparaat dat ontworpen is voor gebruik met een SPI XiP-interface is de AT25SL321-UUE-T van Adesto Technologies (Afbeelding 1). Dit is een Flash-geheugen van 32 megabit (Mbit) dat enkele, dubbele en viervoudige SPI-modi ondersteunt. Het ondersteunt een SPI-klok van 104 megahertz (MHz), die in dubbele SPI-modus een equivalente kloksnelheid van 266 MHz oplevert en in viervoudige SPI-modus een equivalente kloksnelheid van 532 MHz.

Afbeelding 1: de AT25SL321 van Adesto is een Flash-geheugen van 32 Mbit dat enkele, dubbele en viervoudige SPI-modi ondersteunt. Hij biedt 32 Mbit Flash-geheugen in een 8-pins SOIC, DFN8 of TSSOP8 pakket. (Bron afbeelding: Adesto Technologies)

Naast de 32 Mbits Flash heeft het apparaat statusregisters om het apparaat te configureren. Het aflezen van de statusregisters kan de firmware vertellen of het apparaat bezig is met een schrijf- of wisbewerking. Door naar statusregisters te schrijven, kunnen blokken Flash-geheugen worden beveiligd tegen schrijven.

De AT25SL321 van Adesto heeft ook 4 kilobits (Kbits) OTP-geheugen (OTP staat voor one-time programmable, eenmalig programmeerbaar) dat kan worden gebruikt voor het opslaan van beveiligingsinformatie, bijvoorbeeld een uniek serienummer. Leverbaar als 8-pins SOIC, DFN8 of TSSOP8 pakket.

Net als alle andere seriële geheugenapparaten die SPI XiP ondersteunen, is de AT25SL321 van Adesto geconfigureerd met een instructieset die specifiek is voor Adesto-apparaten. De instructieset bestaat uit 38 commando's die door de hostmicrocontroller worden gebruikt om het seriële Flash-geheugen te besturen. Een SPI XiP-randapparaat op een hostmicrocontroller zal een programmeerbare toestandsmachine bevatten die bij het opstarten van de microcontroller wordt geïnitialiseerd met de instructieset van het seriële Flash-targetgeheugen. Eenmaal geïnitialiseerd is de werking van het SPI-randapparaat transparant voor de firmware die de code uitvoert in het in het geheugen toegewezen SPI XiP gebied.

Als de firmware van de hostmicrocontroller bijvoorbeeld data afleest uit het in het geheugen toegewezen gebied, stuurt de SPI XiP die is geconfigureerd met de Adesto-instructieset een instructiecode voor het aflezen van gegevens gevolgd door een 24-bits byte-adres naar het seriële geheugen van Adesto. Het seriële geheugen van Adesto stuurt de geheugeninhoud vervolgens met één byte tegelijk naar de hostmicrocontroller. De firmware ziet dit als normaal aflezen uit het geheugen.

Naast een SPI-klok, data en chip-selectiepinnen, heeft de Adesto AT25SL321 ook twee extra pinnen voor verbeterde interne systeemfunctionaliteit. WP\ is een actieve-lage schrijfbeveiligingspin die schrijven naar de statusregister voorkomt om schrijfbeveiliging van codeblokken te bieden. De microcontroller kan deze pin gebruiken om te voorkomen dat taken met lage prioriteit niet-geautoriseerde wijzigingen doorvoeren. HOLD\ wordt gebruikt om een lopende gegevensoverdracht te pauzeren. Dit kan nuttig zijn als de microcontroller een interrupt-signaal met hoge prioriteit ontvangt terwijl er een gegevensoverdracht naar het geheugen aan de gang is, die moet worden gepauzeerd totdat de interrupt is afgehandeld.

Het AT25SL321 32 Mbit Flash-apparaat van Adesto ondersteunt vier werkingsmodi:

- Standaard SPI werkingsmodus: de toegang tot het Flash-geheugen is als bij een standaard SPI-geheugenapparaat met SPI-klok (SCLK), actieve-lage chipselectie (CS\), seriële invoergegevens (SI) en seriële uitvoergegevens (SO). Standaard SPI-busmodi 0 en 3 worden ondersteund.

- Dubbele SPI werkingsmodus: levert tweemaal de gegevenssnelheid van de standaard SPI werkingsmodus, door SI en SO te gebruiken als bidirectionele datapinnen, aangeduid als IO0 en IO1.

- Viervoudige SPI werkingsmodus: levert viermaal de gegevenssnelheid van de standaard SPI werkingsmodus. Naast IO0 en IO1 worden ook WP\ en HOLD\ als bidirectionele datapinnen gebruikt, IO2 en IO3. In de viervoudige SPI werkingsmodus zijn de WP\ en HOLD\ functies niet beschikbaar.

- QPI werkingsmodus: dit wordt alleen gebruikt voor SPI XiP werking. Waar de standaard, dubbele en viervoudige SPI-modi allemaal het verzenden van commando's aan het SPI-geheugen met alleen de IO0-pin ondersteunen, ondersteunt de QPI-werkingsmodus het verzenden van commando's met gebruikmaking van de vier IO[0:3] pinnen, met een significante verbetering van de prestatie van SPI XiP als resultaat.

Als de 32 Mbits van de AT25SL321 van Adesto niet toereikend zijn, biedt Adesto ook de AT25QL641-UUE-T met 64 Mbit. De twee apparaten zijn pin-compatibel, dus de AT25QL641 kan worden gebruikt als drop-in vervanging. Naast het grotere geheugen is het enige verschil tussen de twee apparaten dat de AT25QL641 bij het opstarten standaard is ingesteld op QPI-werkingsmodus. Dit vermindert de tijd die nodig is voor de set-up in hoogperformante systemen. Beide apparaten trekken gedurende een geheugenafleescyclus slechts 5 milliampère (mA). Beide Adesto-geheugenapparaten werken op een enkele rail van 1,7 tot 2,0 volt en kunnen worden gekoppeld aan iedere willekeurige microcontroller met compatibel voltage die over een SPI XiP-interface beschikt.

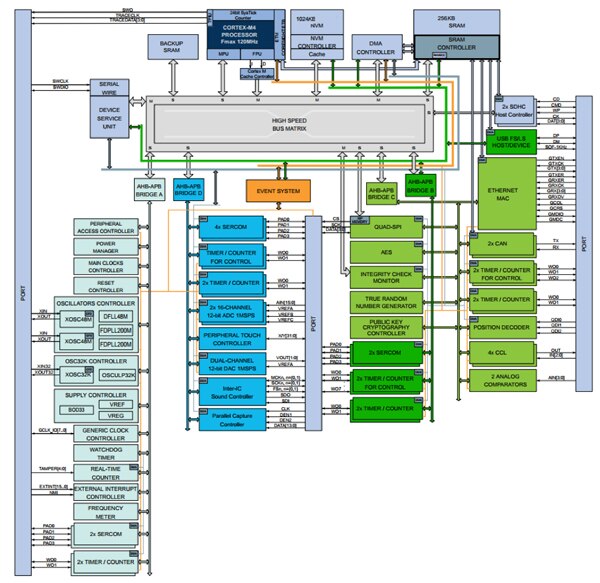

Voor wat betreft de hostmicrocontroller: Microchip Technology heeft SPI XiP-interfaces op zijn ATSAMD51-serie, waaronder de 120 MHz Arm® Cortex®-M4F-gebaseerde ATSAMD51J20A-UUT microcontroller. Dit apparaat heeft 1 Mbyte Flash en 256 kilobytes (Kbytes) RAM. De microcontroller beschikt over een complete reeks van randapparaten, waaronder een analoog-digitaalomzetter (ADC), digitaal-analoogomzetter (DAC), USB-poort en I2S. Daarnaast beschikt hij over een randapparaat voor versleuteling van openbare sleutels en een true random number generator (TRNG) voor beveiligingsfuncties.

Afbeelding 2: de ATSAMD51J20A van Microchip beschikt over een complete set randapparatuur, waaronder een seriële SPI XiP-interface, ADC, DAC en ondersteuning voor gegevensversleuteling. (Bron afbeelding: Microchip technology)

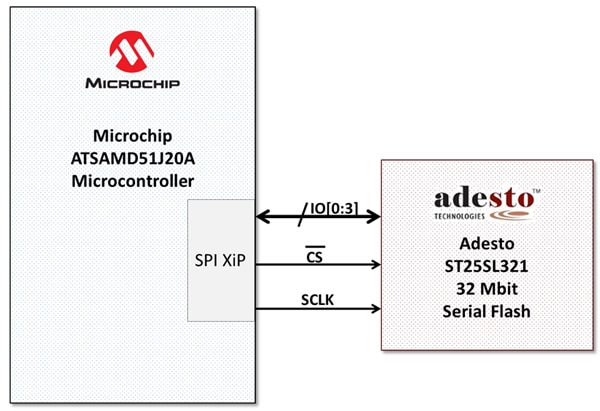

Voor de verbinding met het externe Flash-geheugen kunnen ontwikkelaars het QSPI-randapparaat van de ATSAMD51J20A gebruiken, dat SPI XiP ondersteunt. Dit maakt het mogelijk om de code rechtstreeks vanuit het Adesto Flash-geheugen uit te voeren. De ATSAMD51J20A wijst het Flash-geheugen van Adesto toe in de Advanced High-Performance Bus (AHB) programmageheugenruimte van de Arm. Om gegevens in het seriële Flash-geheugen te beschermen ondersteunt ATSAMD51J20A SIP XiP transparante versleuteling (scrambling) van gegevens die naar het externe SPI-geheugen worden geschreven en ontsleuteling (unscrambling) van gegevens die uit het externe SPI-geheugen worden gelezen. Dit kan helpen bij het voorkomen van ongeoorloofd kopiëren van firmware en systeempiraterij.

Afbeelding 3: de ATSAMD51J20A 32-bits microcontroller van Microchip heeft een QSPI-randapparaat dat een seriële SPI XiP-poort ondersteunt. Dit kan met slechts zes pinnen eenvoudig worden gekoppeld aan het seriële Flash-geheugen AT25SL321 van Adesto. (Bron afbeelding: DigiKey)

Gebruik van de ATSAMD51J20A van Microchip met een serieel Flash-geheugenapparaat van Adesto

Het SPI XiP-randapparaat van de ATSAMD51J20A van Microchip heeft drie registers die worden gebruikt om commando's naar een externe serieel XiP-Flashgeheugen te sturen. Aangezien seriële Flash XiP-geheugenapparaten van andere leveranciers andere instructiecodes gebruiken, moeten deze registers als volgt door de ontwikkelaar worden geconfigureerd voor de specifieke geheugenleverancier:

- Het instructiecoderegister bevat de instructie die wordt gebruikt om toegang tot het seriële Flash te krijgen. Voor een Flash-geheugenappaaat van Adesto dat in viervoudige SPI-modus werkt, bevat dit register een instructie 'Fast Read Quad Output' 0x6B indien de firmware de code uitvoert vanuit het in het geheugen toegewezen XiP-gebied. Dit register moet in de juiste instructiecode worden veranderd indien een schrijf-, wis- of statusregisterbewerking wordt uitgevoerd.

- Het instructie-adresregister bevat het adres van het Flash-geheugen waartoe toegang wordt verkregen in het externe seriële Flash-geheugen. Wanneer de ATSAMD51J20A SPI XiP van Microchip is geconfigureerd voor de seriële geheugenmodus, wordt dit adres door het SPI XiP-randapparaat automatisch ingesteld op het adres dat wordt uitgevoerd door de firmware in het in het geheugen toegewezen AHB geheugenruimtebereik 0x0400 0000 tot 0x0500 0000.

- Het instructieframeregister configureert de SPI XiP voor het instructieframeformaat dat specifiek is voor het gebruikte externe geheugenapparaat. Dit omvat selectie van de adreslengte van 24 of 32 bits, activering van double-data rate (DDR), of continue leesmodus wordt ondersteunt en de lengte van de opcode.

De rest van de SPI XiP-interface van Microchip kan gemakkelijk worden geconfigureerd met de SPI-drivers van Microchip.

Zolang de toepassingsfirmware op de microcontroller de code vanuit het in het geheugen toegewezen SPI XiP gebiedt uitvoert, hoeft het SPI XiP-randapparaat op de microcontroller niet opnieuw te worden geconfigureerd. Het Flash-geheugen van Adesto ondersteunt ook een leesmodus met alleen de enkele SI-pin met instructiecode 0x03. Als alleen de dubbele SPI-modus wordt gebruikt, is de instructiecode 0x3B. Deze codes worden door toepassingsfirmware naar het instructiecoderegister geschreven.

Het is een goede gewoonte om alle caches die geassocieerd zijn met de toegewezen geheugenadresruimte leeg te maken wanneer het instructiecoderegister wordt gewijzigd. Bij het lezen of schrijven naar de statusregisters van het seriële Flash-geheugen, dient de cache te worden leeggemaakt en vervolgens uitgeschakeld. Dit moet ook worden gedaan bij het schrijven naar het Flash-geheugen in de in het geheugen toegewezen gebieden. De cache moet opnieuw worden ingeschakeld zodra de geheugenleesbewerkingen worden hervat.

Vanwege de hoge snelheid van de gegevensoverdracht, moet het seriële Flash-geheugen op het pc-bord zo dicht mogelijk bij de SPI XiP-poort van de microcontroller worden geplaatst. Als dat niet mogelijk is, mag geen enkele trace langer dan 120 millimeter (mm) zijn. Het kloksignaal moet op een afstand van minstens driemaal de breedte van de pc-bord traces van andere signalen worden gehouden om interferentie te vermijden. De IO[0:3] bidirectionele datasignalen moeten allemaal binnen 10 mm van elkaar liggen om skew te vermijden.

Conclusie

Externe seriële Flash-geheugenapparaten kunnen een snelle firmware-codeuitvoering bieden zonder de complexiteit en overmatige hoeveelheid ingenomen bordruimte die parallelle Flash-chips met zich mee brengen. Dit maakt eenvoudige uitbreiding van de programmacode in de loop van de tijd mogelijk, evenals updates in het veld zonder de systeemkaart opnieuw te ontwerpen.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.